# Power Integrity Analysis and Management for Integrated Circuits

# Raj Nair • Donald Bennett

Prentice Hall Modern Semiconductor Design Series Prentice Hall Signal Integrity Library Many of the designations used by manufacturers and sellers to distinguish their products are claimed as trademarks. Where those designations appear in this book, and the publisher was aware of a trademark claim, the designations have been printed with initial capital letters or in all capitals.

The authors and publisher have taken care in the preparation of this book, but make no expressed or implied warranty of any kind and assume no responsibility for errors or omissions. No liability is assumed for incidental or consequential damages in connection with or arising out of the use of the information or programs contained herein.

The publisher offers excellent discounts on this book when ordered in quantity for bulk purchases or special sales, which may include electronic versions and/or custom covers and content particular to your business, training goals, marketing focus, and branding interests. For more information, please contact:

U.S. Corporate and Government Sales (800) 382-3419 corpsales@pearsontechgroup.com

For sales outside the United States please contact:

International Sales international@pearson.com

Visit us on the Web: informit.com/ph

Library of Congress Cataloging-in-Publication Data

Nair, Rajendran.

Power integrity analysis and management for integrated circuits / Rajendran Nair, Donald Bennett.

p. cm.

Includes bibliographical references and index.

ISBN-13: 978-0-13-701122-3 (hardback : alk. paper)

ISBN-10: 0-13-701122-9 (hardback : alk. paper)

Integrated circuits—Design and construction—Quality control. 2. Signal integrity (Electronics)

Power electronics. I. Bennett, Donald, 1959. II. Title.

TK7874.58.N35 2010

621.3815—dc22

2010003453

Copyright © 2010 Pearson Education, Inc.

All rights reserved. Printed in the United States of America. This publication is protected by copyright, and permission must be obtained from the publisher prior to any prohibited reproduction, storage in a retrieval system, or transmission in any form or by any means, electronic, mechanical, photocopying, recording, or likewise. For information regarding permissions, write to:

Pearson Education, Inc. Rights and Contracts Department 501 Boylston Street, Suite 900 Boston, MA 02116 Fax: (617) 671-3447

ISBN-13: 978-0-13-701122-3 ISBN-10: 0-13-701122-9 Text printed in the United States on recycled paper at Edwards Brothers in Ann Arbor, Michigan. First printing, April 2010

# PREFACE

This book is our earnest and first effort at demystifying power integrity, its detailed analysis, and its management for integrated circuits in the nanometer scale era.

The focus of the book is squarely on integrated circuits and power integrity as it pertains to such components. It is intended both for the student engineer gaining an introduction to the field of integrated circuit design, and for those skilled in the art, developing systems based on integrated components. Hence, every attempt has been made to emphasize basic concepts, principles, and intuitive understanding, while also discussing state-of-the-art and advanced concepts and technologies. This book differs from prior, related efforts at least in that it emphasizes comprehensive, *true-physical* modeling of integrated circuits and systems behavior. Beginning with an intuitive understanding of power integrity in a fundamental, physical sense, through analogies with mechanical systems and their underlying laws, we explore root causes for a rise to predominance of power integrity as a performance differentiator for integrated circuits.

A simple example is helpful in establishing the importance of power integrity to integrated circuits and systems. Today, as integrated systems become increasingly powerful and portable, system and device power and energy consumption is a critical design constraint. But less noticed is power integrity, despite its principal role in determining power consumption. Most of us notice that if we dim the lights in our entertainment rooms too much, sharp changes in brightness of our television screens hurt our eyes. Our attempt to reduce lighting energy consumption therefore depends directly on the level of light noise we encounter. The very same is true for integrated circuits: minimization of power and energy consumption through supply voltage reduction, a fundamental approach, depends directly on knowing the level of power supply noise, or, in other words, power integrity.

We must nevertheless confess that motivation for this work comes in large part from power integrity studies into high-performance microprocessors rather than from a need to save energy in low-power, system-on-chip components. While engaged in the investigation of technologies for future generations of processor packages, we observed a lack of tools enabling the determination of the spatiotemporal coincidence of power supply noise with critical path activation within circuits. Optimization of the placement of power integrity management components such as package capacitors remains an afterthought in package design. Nonphysical approximations such as simplified resistance-capacitance models are commonly employed in the analysis of a chip power distribution network. It is well known that the extraction of key electromagnetic aspects of on-chip interconnect, or resistance, capacitance, and inductance, and simulation of such extracted models with circuit blocks and system-level components, are tasks of high and increasing computational complexity. Hence, optimization of on-chip power grids, circuit block placement, and decoupling capacitance allocation also suffers in quality. More importantly, we see an absence of early, front-end tools for allocation of chip resources such as metal, decoupling capacitance, and external connectivity such as power supply pads with respect to power integrity performance. This constrains quality and degrees of freedom in physical design, often leading to overallocation of chip resources, or excessive iterations of design. With many additional challenges in nanometer-scale fabrication processes, we see this absence of comprehensive, true-physical investigation, and of front-end analysis capability for power integrity, to be significant challenges to continued scaling of integrated devices.

We have therefore endeavored to put into book form our learning and investigations over the past decade into this important aspect of integrated circuit design. Our work in this field has taught us that high levels of abstraction and physics-based modeling and analysis addresses many of the challenges of power integrity. This learning is captured in the book, along with traditional and advanced methods and techniques for power integrity analysis.

While we discuss many necessary aspects of power, power integrity, power supply, and distribution network design, as well as power integrity management,

this book is, quite simply, only an introduction to this complex topic. Discussions within may at times appear to be too brief, or, occasionally, overly laden with details and exemplary illustrations, and at times even appear to be repetitive. While many readers will grasp the principles and theory discussed readily, we believe lay readers will find additional explanations, examples, and reiteration within helpful. Readers of all levels will appreciate some of our exercises designed to invoke thought beyond the teachings of chapter material. The book is meant to provide a fuller understanding of power integrity as it relates to integrated circuits, and strives to focus on derivations from first principles as well as intuitive understanding. Empirical understanding is also provided in places within along with our considered inferences where appropriate.

We humbly opine that as researchers ourselves, we are fallible; we've ventured to discuss concepts in this book that are not yet in common use, which must therefore be applied by our readers after diligent and thorough validation in their work. Skilled practitioners nevertheless will, we believe, find the advanced concepts discussed in this book resonating well with their own efforts, and, on occasion, to be surprising discoveries advancing their learning. For instance, we discuss differential power distribution as a "broadband" power supply distribution method. Signal integrity engineers may readily appreciate the similarities that this concept shares with differential signal transmission, which has all but replaced single-ended signaling. We also discuss active noise regulation, a technique that dynamically changes network impedance at a power grid junction, enhancing power integrity. These and other concepts and techniques, as for example, *holistic integration*, and the constructive employment of supply undulations to benefit circuit performance through dynamic timing analysis, are proposed with confidence but not necessarily with sufficient prior implementation and empirical evidence. We hope readers and researchers will find these concepts as intriguing and enlightening as they have been to us.

# **Book Organization**

At a high level, the book is organized into four distinct parts. The first part, comprising Chapters 1 to 3, provides a foundational understanding of power integrity, the challenges posed for power and power integrity by relentless scaling, practical aspects of power delivery, and the beneficial application of *total power integrity* to chip physical design optimization. Chapters 4 through 7 form the second part, which focuses on various aspects of power distribution network modeling, design, and analysis. These chapters highlight abstraction and physics-based analysis while also providing copious discussion of traditional circuit- and field-solver-based techniques. The third part concentrates on floorplanning and implementation of various techniques for power integrity management. Chapters 8 and 9 comprise this part of the book, and discuss advanced power integrity management concepts and implementations. Chapter 10 closes the book with a discussion on integration trends and the consequent challenges for power integrity. Brief descriptions of the individual chapters and recommended reading strategies follow.

Chapter 1, "Power, Delivering Power, and Power Integrity," employs physical analogies to develop an intuitive understanding of power and aspects of power integrity. For instance, the *force-voltage analogy* is used to relate work done, power, and energy in electrical form to the same quantities in the physical world. Beginning readers in the field will find this chapter helpful in developing an appreciation for power integrity, whereas skilled practitioners may wish to skip the chapter, or skim through it to review and refresh some salient points.

Chapters 2 and 3 are essential segments of the first part of the book, recommended for both beginning experimenters and skilled practitioners of the field. Chapter 2, "Ultra-Large-Scale Integration and Power Challenges," delves deeply into fundamental aspects of CMOS scaling and *energy-delay*, illustrating through simple derivations differences between *nanoscale* and prior integrated circuit fabrication regimes. This chapter sets a foundation for discussions on total power integrity including inductive aspects of chip power grids by demonstrating potential follies ensuing from the exclusion of inductance in signal propagation analysis as it relates to energy and circuit performance. The chapter also derives scalingdriven relationships for power integrity and system aspects that influence it directly. Chapter 3, "IC Power Integrity and Optimal Power Delivery," discusses power delivery and IC power distribution, and in particular, details distributed voltage regulation as well as a connection between switched, efficient power conversion and scaling. These chapters firmly establish the significance of on-chip inductance to chip power grid design, and provide methods for its incorporation into power integrity analysis.

Chapters 4 through 7, recommended for readers of all skill levels in the field, discuss various techniques for power distribution network modeling and analysis in much detail. Chapter 4, "Early Power Integrity Analysis and Abstraction," details *front-end analysis* and abstraction based chip and power distribution network modeling. Chapter 5, "Power Integrity Analysis and EMI/EMC," begins with a detailed description of traditional power distribution network modeling and impedance management, discusses modeling methods and numerical analysis, and

Preface

establishes the importance of, and accuracy in, 3D field-solver-based methodologies. The chapter then illustrates the application of such analysis methods to exploring the close relationship between power integrity and electromagnetic radiation in chip packages. It again highlights the need for comprehensive, systemlevel, and early analysis of power integrity as well as EMI. Chapter 6, "Power Distribution Modeling and Integrity Analysis," presents a modeling technique that employs distributed *RLC* elements for accurate and efficient on-chip power distribution analysis, and applies the technique to a case study demonstrating the effects of different power supply noise reduction techniques. Chapter 7, "Effective

Current Density and Continuum Models," describes a novel modeling method that permits the abstraction of a power distribution grid into a continuum model of greatly reduced computational complexity. The chapter includes numerous illustrative examples demonstrating benefits of abstraction-based modeling in chip floorplanning, and compares a continuum model-based simulator with SPICE.

Chapters 8 and 9 combine state-of-the-art and advanced methodologies and concepts developed in the industry for power and power integrity management, as well as power-integrity-aware floorplanning. Chapter 8 in particular focuses on chip floorplanning and design with power integrity awareness, and discusses the impact of power management techniques on power integrity. Chapter 9 details chip- and package-level power integrity management techniques, exploring advanced techniques such as decoupling capacitance *channel length design*, triple-well fabrication processes, *voltage-dependent capacitance*, and *active packaging*. These chapters are recommended reading for practicing and experienced engineers.

Chapter 10 forms a brief, closing segment of the book, discussing advanced technologies and trends for continued device scaling and electronics integration. Readers will find ample evidence for integration moving into the third dimension through silicon and packaging technologies in this chapter. Integration driven by miniaturization and cost-reduction requirements is described in detail, with implications to power, heat, and power integrity challenges highlighted.

# **Supporting Material**

Appendices included in the book assist by providing further detail for derivations or theory in the more mathematical chapters of the book. Appendix A is the complete derivation of the *Effective Current Density* based continuum modeling approach to conducting grids. Appendix B provides a derivation of the Helmholtz equation for planar circuits.

Internet links dispersed throughout the book are intended to provide readers with ready access to advanced simulation results visualization as well as online reference documents. In like manner, footnotes throughout all chapters provide readers with ready clarification of uncommon terms or concepts.

The continuum model based power grid simulator employing abstraction for chip power grid, circuit blocks, and capacitance, RLCSim.exe, is freely available from Anasim at the web link: http://www.anasim.com/category/software/. This Microsoft Windows compatible software comes with a manual and a set of examples including some experiments of Chapter 4.

## **Further Learning**

Other texts in this area, listed early among the references in Chapter 9, provide excellent treatment of printed circuit boards, planes, passive components, transmission lines, and related circuit behavior. We hope that our unwavering focus on integrated circuits and power integrity in this book will complement these other works well, while paving the way for further investigations into advanced analysis methods and power integrity management. Advancement in power integrity modeling and analysis capability as discussed within will be key to facilitating sustainable, 3D, and holistic integration in the nanoscale regime. It is with this belief that we offer our work and learning to you as stepping stones to further learning and accomplishment.

*Raj Nair Donald Bennett* Anasim Corporation

# CHAPTER 1

# **Power, Delivering Power, and Power Integrity**

*Power* may be defined as the capacity to perform work, and is measured as the work done or energy transferred per unit of time. The greater the power, the greater the capacity to move something (against forces of attraction, repulsion, or friction) or to transfer energy (by raising the temperature of a substance, for example). With reference to electronic systems, and integrated circuits in particular, power is the presence of voltage, or electromotive force, and current, or the flow of charge. Power enables the performance of desired functions in the system and is delivered by devices that generate, store, or regulate electromotive force or flow of charge. Electronic circuits and systems consume this delivered power and convert it into other desired forms of energy or activity. The integrity of delivered power relates to its stability and invariability through variations in energy expenditure, in transfer elements, in the generating source, or in the surrounding environment. These aspects are expounded on in the following sections of this chapter, with a focus on integrated circuits and systems.

#### 1.1 Electromotive Force (emf)

The discovery of electromotive force is attributed to physicist Alessandro Volta (1745–1827), who invented the electric battery or voltaic pile. Electric batteries possess the ability to move electric charge. They perform work, a prerequisite of which is the existence of force; batteries are therefore termed sources of electromotive force or *emf*.

The unit of emf is the *volt*, and as defined in the international system of units, one volt equals one *joule* per *coulomb*, where *joule* is the unit of energy and

*coulomb* is the unit of electrical charge. Viewed another way, if a charge of a coulomb gains a joule of energy in passing through a device, the emf present across the device is a volt.

Since the movement of charged particles and gain (or loss) of energy is involved, mechanical analogies are often employed to illustrate aspects of electrical behavior such as *emf*, current, and power. The *force-voltage* analogy is a common example, wherein mechanical force is equated to electrical voltage.

#### 1.1.1 Force-Voltage Analogy

The force-voltage analogy [1] is attributed to James Clerk Maxwell.<sup>1</sup> Since the SI (French *Le Système International d'Unités*, or International System of Units) unit of force is the *newton*, and the unit of emf is the volt, this analogy is not altogether consistent. Nevertheless, many aspects of electrical behavior mirror the behavior of physical objects, and such an electrical-mechanical analogy assists comprehension. An electrical "tank" circuit, for example, behaves in much the same way as the pendulum of a mechanical clock.

Work done, whose SI unit is the joule, involves force and distance. Hence:

$$W(joules) = F(newtons) \cdot d(meters)$$

(1-1)

Similarly, voltage difference, or electrical potential difference, in a homogeneous medium, is the work in joules required to move a coulomb of charge from a point to another. Therefore:

$$V(volts) = \frac{W(joules)}{Q(coulombs)}$$

(1-2)

If one associates force with voltage, following the relationships above, *dis-tance* in mechanical terms will be equivalent to *charge* in electrical terms. Distance over time, or *velocity*, will be equivalent to charge transferred over time, or *current*.

<sup>1.</sup> James Clerk Maxwell, Scottish theoretical physicist and mathematician, 1831-1879. [2]

Consider the expression for kinetic energy:

Kinetic Energy =

$$\frac{1}{2}mv^2$$

(1-3)

where m is the mass and v the velocity of the object. Also consider the expression for energy stored in a magnetic coil:

Energy of an inductor

$$=\frac{1}{2}LI^2$$

(1-4)

where L is the inductance of the magnetic coil, and I the current flowing through the coil. These expressions suggest an equivalence between *mass* and *inductance*.

The *distance* moved by an elastic spring increases the energy stored within it and linearly increases its force of resistance. Similarly, *charge* transferred into an electrical capacitance device increases the energy stored in the capacitance, and linearly increases emf across its terminals. Work done on a spring, or an increase in its potential energy, is given, following *Hooke's Law*, by:

Spring

$$PE = \frac{1}{2}kx^2$$

(1-5)

where k is the elastic constant of the spring and x the elongation or compression. This relationship is equivalent to that for electrical potential energy stored in a capacitor:

$$Capacitor \ PE = \frac{1}{2}CV^2 \tag{1-6}$$

The equivalence is to an extent hidden within these expressions, since V does not correspond to x. The expression for potential energy in a spring may be derived by the integration of force (given by Hooke's Law as  $k \cdot x$ ) over distance traversed (dx), which derivation is left to the reader. Hence, the expression for potential energy is obtained from force • distance (( $k \cdot x$ ) • x), as in the fundamental definition of work done. Similarly, the expression of potential energy in a capacitor is derived from voltage  $\cdot$  charge ( $V \cdot (C \cdot V)$ ), which also follows from the definition of work done in electrical terms, in a manner consistent with the force-voltage analogy.

It is also useful to note the equivalence of energy in static and dynamic analysis of fluid flow to electrical energy, since electric current may be described as a fluid-like flow of electrons or charge at a macroscopic level. Gravitational potential energy is given by  $m \cdot g \cdot h$ , where m is mass, g is acceleration due to gravity, and h is the height increase. In an analogy with liquids, it is common to equate pressure at the bottom of a liquid column with emf. A conduit joining two columns of different diameter, but of the same height and fluid matter, will see no fluid flow since fluid pressure will be the same at both ends of the conduit. This example is equivalent to two capacitors of different capacitance value charged to the same electric potential. If the column heights are different, a flow of liquid between the two columns will be established through the conduit, subject to its diameter. The electrical equivalent to this physical analogy is the relationship between emf, or voltage, and charge flow, or current, as presented by *Ohm's Law:*

$$I(amperes) = \frac{V(volts)}{R(ohms)}$$

(1-7)

where R, or *resistance*, is the property by which materials oppose or resist the flow of charged particles through their atomic structures. Resistance is a property that leads to energy absorption. It is also a property that leads to loss of emf in an electrical circuit, since:

$$V = I \bullet R \tag{1-8}$$

whereby some electromotive force is spent in overcoming the resistance of a connecting element to the flow of charges through it, much as force is spent overcoming friction in mechanical systems.

Another analogy sometimes used is the force-current analogy, in which an electrical current source is equated with a force generator, and voltage equated with input velocity to a mechanical system. This analogy results in capacitance being equated to mass, inductance to the inverse of the spring constant, and resistance to the inverse of friction [1].

#### **1.2 Electrical Power**

Electrical power is defined as the product of voltage and current, where the latter is the rate of flow of electric charges, represented by *I* or *i*. The SI unit of current is the *ampere*. Instantaneous power, therefore, is the product of instantaneous voltage and instantaneous current, or:

$$P_i = v \bullet i \tag{1-9}$$

Instantaneous power  $P_i$  is often averaged over a representative time duration to yield average power. In alternating current systems with sinusoidally varying potentials, instantaneous voltages and currents are often vectors with a phase angle difference, leading to:

$$P_{i,ac} = V\sin(\omega t) \cdot I\sin(\omega t - \phi) \tag{1-10}$$

where V and I are amplitudes or peak absolute values for voltage and current,  $\omega$  is the vector angular velocity, and  $\varphi$  is the phase difference between voltage and current vectors. Solving further using known trigonometric relationships [3], we find:

$$P_{i,ac} = \frac{VI}{2} (\cos(\phi) - \cos(2\omega t - \phi)) \tag{1-11}$$

which, when averaged over one or more cycles, given that the average of any sinusoidal function over its period is zero, yields:

$$P_{ac,avg} = \frac{VI}{2}\cos(\phi) \tag{1-12}$$

which may also be written as:

$$P_{ac,avg} = V_{rms} \bullet I_{rms} \bullet \cos(\phi)$$

$$V_{rms} = \frac{V}{\sqrt{2}}, I_{rms} = \frac{I}{\sqrt{2}}$$

(1-13)

where  $V_{rms}$  and  $I_{rms}$  are the root-mean-square or "effective" values of voltage and current, respectively. The cosine of the phase angle between the alternating voltage and alternating current is also called the *power factor*, or the factor by which the product of effective voltage and current must be multiplied to yield true alternating current (AC) power. For current flow that is 90 degrees or one-quarter cycle out of phase with voltage, the power factor is 0.

Multiplication of the current vector with the power factor yields the component of the current vector in phase with the voltage vector: It is only this component that results in power delivered or consumed. Orthogonal relationships between voltage and current vectors, which exist in purely reactive components such as ideal capacitors and inductors, therefore do not result in power consumed, though large currents may flow through such components in response to applied alternating or otherwise varying voltages.

#### 1.2.1 Physical Analogy for Power

Electrical *power* is the product of voltage and current, where the latter is charge transferred over time. Following the force-voltage analogy in our earlier discussion in this chapter, power should be equivalent to force applied for a distance over time, or a velocity (rate) at which force is applied and work done. This provides an intuitive definition for power as the rate at which energy is absorbed or produced. The greater the power, the greater the capacity to provide energy, and the greater the rate at which energy is absorbed or consumed.

The SI unit of power is the *watt*, with the symbol *W*. If 1 joule of work is done in 1 second, the power consumed is 1 watt. Following this definition, and from the earlier relationship between voltage, work, and charge:

$$Power(watts) = \frac{W(joules)}{t(seconds)} = \frac{V(volts) \cdot Q(coulombs)}{t(seconds)} = V \cdot \frac{Q}{t} = V \cdot I(amperes) \quad (1-14)$$

By the same definition, energy, or work done, is the product of power and time. Higher power consumption therefore leads to higher energy absorption in a unit of time. This is demonstrated physically in the heating of materials. Higher power directly translates to faster increases in temperature and greater heat buildup.

#### 1.2.2 Sources of Electrical Power

Electrical energy and power can be generated in numerous ways. Natural electrical energy is generated through *static electricity*, or the physical separation and

#### **Electrical Power**

transport of charges, resulting in lightning and the commonly observed crackles in everyday objects that rub against each other. Static electricity has been employed in Van de Graaf generators [2] to produce more than a million volts.

The most common method of electricity generation is electromagnetic induction, where mechanical energy is employed to turn an electrical generator. Sources of mechanical energy include nuclear energy, solar thermal energy, the flow of water, wind, ocean tides, and even ocean waves. The other common method of electrical energy generation is through electrochemistry, or a direct conversion of chemical energy into electrical energy, as seen in electric batteries and fuel cells. Photovoltaic conversion, the transformation of energy in sunlight directly into electrical energy, is now widely employed as well. Supercapacitors, with extremely high energy storage density, often replace or augment electric batteries. Other forms of electricity generation are thermo-electricity, a direct transformation of heat into emf in thermocouples, and piezo-electricity, a transformation of mechanical strain in crystals into electricity. These energy conversion devices are employed primarily as sensors, though some are used in energy harvesting, a process in which energy is extracted from the ambient environment to provide electrical power to small, autonomous devices. Radio frequency (RF) fields are also now used to harvest small amounts of energy.

## 1.2.3 Powering Electrical and Electronic Circuits and Systems

All electrical and electronic systems function using electrical energy. These systems now exist in tremendous variety, assisting human activity in every manner imaginable. They employ electrical energy to perform useful work, transforming energy into other forms, such as motion (kinetic energy), light (visible electromagnetic energy), and heat (thermodynamic energy). They may also alter quantities of electrical energy, producing higher or lower potential differences and periodically varying potential differences.

Different systems are designed to employ different forms of electrical energy. Most large machines are designed to function using the alternating current (AC) form of electrical energy. Due primarily to its ease of transformation and transmission, AC was deemed most suitable for the transmission of electrical energy from generating stations to distributing stations and end users. Traditional lighting systems, such as incandescent lamps and fluorescent lamps, are designed to operate using AC electrical power. Many household machines are also designed to run using AC voltages reduced to a relatively safe level. Such AC electrical power employs a frequency of 50, 60, or 440 cycles per second, and an amplitude from 110 V to 240 V or higher. AC power is often provided with multiple phases,

or alternating voltages shifted in phase angle from each other, typically in three phases 120 degrees apart. Systems employing AC power are generally called "electrical" systems.

Electronic systems typically operate with *direct current* (DC, previously called *galvanic current*) electrical power. DC electrical power is characterized by a constant voltage (or potential difference supplied) and a unidirectional flow of electric charge. Most such systems operate at low voltage values that are one to two orders of magnitude below amplitudes common in AC electrical power. AC electrical power is readily convertible into DC through *rectifiers, DC-to-DC converters,* and *filters.* Nowadays, DC can also be readily converted into AC through electronic systems called *inverters.* High-voltage direct current is sometimes employed to transmit large amounts of power from remote generation sites or to interconnect AC power grids. DC power is also finding greater use in energy-efficient solid-state lighting.<sup>2</sup>

Our discussion in succeeding sections and chapters will focus on direct current electrical power as the predominant form of electrical power energizing electronic systems, with specific reference to integrated circuits and systems.

## 1.3 Power Delivery

Electrical power is delivered in two distinct ways, through *conductive coupling* and through *electromagnetic coupling*. In conductive coupling, power is transferred through electric conduction or physical transfer of charges from one body to another through a conductive medium. In the electromagnetic coupling method, power is transferred through electromagnetic induction or communication, where charges are induced to move in the presence of electromagnetic energy.

This distinction is useful in differentiating DC power from AC power; all direct current power is delivered through conductive coupling, while AC power may be delivered through either method. Examples of AC power delivered electromagnetically include Nikola Tesla's 1893 demonstration of wireless energy transfer used to illuminate vacuum bulbs, and William C. Brown's demonstrations of power transmission using microwaves from 1961 to 1964. Ordinary transformers are everyday examples of AC power delivery through electromagnetic coupling. Electrochemical batteries and wires connecting to a circuit are demonstrations of conductively coupled DC power.

Light generation using electronic components such as light emitting diodes (LEDs) instead of the more common incandescent or fluorescent lamps.

#### 1.3.1 Central DC Power Delivery Module

Figure 1-1 shows a power supply module integrated in a personal computer system. Most such power supply modules in stand-alone electronic systems convert available AC power into a number of distinct DC voltages that serve other modules in the system. In the illustrated module, for example, DC voltages of +12 V, -12 V, and 5 V are generated from AC power entering through the chassismounted socket seen above the switch. These voltages power subsystems such as a hard disk drive or a microprocessor motherboard. Such a power delivery system is *central*, developing necessary DC voltages at a dedicated location and distributing them within the system through wires seen leaving the central module.

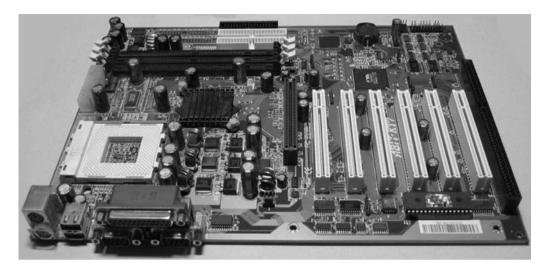

Figure 1-2 shows a motherboard seating a microprocessor, memory, and peripheral cards in a typical personal computer system that integrates the power supply module seen in Figure 1-1. An output connector from the power supply plugs into a connector seen near the middle of the left side of the board. Just below this connector, the board seats a microprocessor on an approximately square socket. To the right of this socket, there are electronic components—transistors,

**Figure 1-1** Example of a power supply module in a personal computer conversion. Source: Author *mboverload*, Wikimedia Commons. [4]

**Figure 1-2** Personal computer motherboard housing a microprocessor and including adjacent DC-to-DC conversion. Source: Gary Houston, Wikimedia Commons. [4]

magnetic-core inductors, and electrolytic capacitors—that perform a further conversion of the DC power supply into a voltage that the microprocessor can use. Such power conversion at or very near the receiving component is called *point-ofload* (POL) power conversion.

This concept originates in the days of the "War of Currents" between Tesla and Edison, when Tesla showed that transporting remotely generated AC power at high voltages, converted to lower voltages where necessary, rendered the distribution of power over large geographic areas very feasible. Tesla solved the problem of energy loss due to high currents in the transmission pathways; a similar problem is solved in electronic systems by the use of POL power conversion. Microprocessors, operating at voltages approaching 1 volt, consume large amounts of current, of the order of 100 amperes or more. If transmitted through the wires of the power supply module, this would lead to unacceptably large voltage and energy loss among other difficulties. In the subsystem of Figure 1-2, power conversion takes place adjacent to the microprocessor, ensuring that high currents only flow across a very short distance of board interconnect.

Microprocessor POL power delivery is commonly performed through voltage regulator modules (VRMs [2]) that communicate with voltage-level control logic within the chip. A VRM is essentially a voltage down-converter, also called **Power Delivery**

a *buck* regulator, that obtains a DC voltage of 12 or 5 volts and converts it to the voltage required by the microprocessor. This conversion is accomplished through high-efficiency switched voltage regulation, as discussed in Chapter 3, Section 3.1.2. VRMs may be replaceable or may be soldered to the motherboard, and are often optimized to work with a specific microprocessor.

#### 1.3.2 Integrated Power Delivery

*Integrated power delivery* is a method whereby power conversion and delivery are integrated with load circuits. Methods of integration vary; examples include in-package voltage regulation,<sup>3</sup> monolithic integrated power conversion,<sup>4</sup> and three-dimensional integration of power delivery circuits with load integrated circuits.

Advantages of integrated power delivery include extremely short lengths of interconnect between power conversion and load components, resulting in reduced energy losses, as well as the potential for faster, symbiotic functionality of the power conversion system and the load device. In recent years, integrated power conversion and delivery has enabled substantial energy savings for integrated circuits through techniques such as *dynamic voltage scaling* and *adaptive voltage scaling*. Integrated power delivery assists in improving power integrity.

#### 1.3.3 Power Distribution Networks

A power distribution network is formed by the interconnection of electrical devices that transfer power from a source to a load. Its principal function is to effectively transfer electrical power from the source to the load, doing so with minimal energy loss and minimal degradation of the power delivered.

As discussed in Section 1.1.1, energy loss in its simplest form is encountered in overcoming opposition to the flow of charge in conducting materials. For a simple direct current source and load, the power distribution network is designed to minimize resistance in the connecting electrical pathways. Depending on the nature of the source and load, more complex power distribution networks are often required. For example, the DC energy source may be derived from an AC input, through rectifiers that make current flow unidirectional. Voltage varies substantially in such a DC energy source, due to the sinusoidal variation of AC voltage waveforms from 0 to peak amplitudes. Such variation may well be unacceptable to the load, and the rectifier's DC output may require further conditioning. This

<sup>3.</sup> The Intel 486 DX4, which required a 3.3 V operating supply, employed an on-package voltage regulator (OPVR).

<sup>4.</sup> Intel 80296SB and 80196NV employed monolithic integrated voltage conversion from 5 V to 3.3 V. [5]

conditioning is performed by *filters* and supply *decoupling* devices. These devices block or bypass variations in energy transmission and smooth out power supplied to the load. Filters and decoupling devices are comprised of capacitors and inductors; capacitors, most commonly employed as supply filtering or decoupling devices, are discussed in later chapters.

#### 1.3.4 Power Delivery Regulation

A key aspect of power delivery is providing electrical power in a controlled or regulated manner. Electrical circuits perform predictably when the supplied voltage and current are regulated according to their needs. Voltage regulation is most common in DC electrical systems, permitting load devices to extract as much current and power as changing conditions may require. Some applications, such as the charging of electrical batteries, require regulated current flow.

A voltage regulator is in many ways similar to a voltage source, such as a voltaic pile, that provides a fixed potential difference. The regulation function keeps the output voltage constant while load currents change, whereas the output of a typical voltage source drops by the product of the drawn current and a finite impedance intrinsic to the source. As drawn load currents increase, a regulated voltage also drops in value but to a much smaller extent. This characteristic is represented in the definition of *load regulation*, which is the ratio of the variation in output voltage, from minimum to maximum drawn load current, to the nominal voltage. *Load regulation* is an indication of the load-bearing quality of the voltage regulator. It is improved through feedback of the load voltage.

Voltage regulation, particularly in DC systems, is accomplished either by switched conversion or linear regulation. In a previous section discussing central and POL voltage regulation, we noted that power conversion near the load minimizes the distance over which high currents flow, thereby minimizing energy loss. This is an important aspect of voltage regulation as accomplished through switched DC-DC power converters. Load requirements of high currents at low-supply voltages are translated into much lower currents drawn from highvoltage supplies. This permits the connection of varied load devices to any given DC voltage source, as long as the power output capacity of the DC source is not exceeded. Switched DC-DC converters are also capable of "boosting" output voltage, providing high voltages at low currents, while drawing power from low voltages at high currents. Additionally, since switched converters employ active devices as switches, energy losses are typically very small as compared with linear regulators, where energy loss is directly related to the product of load current and the difference between input (higher) and output voltages. Hence, switched power converters and voltage regulators are very efficient, approaching 95% efficiency in commercial designs. Due to these advantages, switched power regulation is the most common method employed today, while linear regulation powers systems that demand high bandwidth and an absence of the output ripple inherent in switched converters.

Voltage regulation is the most common example of regulated power delivery, and it assists in maintaining the required voltage across a load. Practical loads will, however, impose significant challenges to any regulated power supply system. A resistive load applied to a DC-regulated power source, in the instant of application, will demand a near-instantaneous rise in current supplied by the power source. This "transient" or fleeting operational requirement may well exceed the capabilities of the power source, whose output voltage may not remain steady during such an event. Such considerations of the reliability and robustness of supplied power are generally categorized under *power integrity*.

#### 1.4 Power Integrity (PI)

In its most common use, *power integrity* refers to the closeness of a power supply to its ideal, or a constant voltage supply, despite changes in power input or load power consumption.

In DC systems, an ideal power supply will maintain a constant output potential difference regardless of load conditions. Practical power supply characteristics—such as load regulation, bandwidth limitations, maximum output capability, delivery network impedance, etc.—result in significant deviations of the output voltage from the ideal.

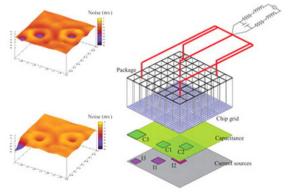

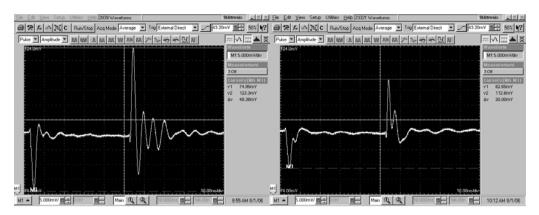

Figure 1-3 displays some manifestations of a nonideal power supply in a field programmable gate array (FPGA), a common integrated circuit implementation. An FPGA is a very versatile and useful integrated circuit that can be programmed to modify functionality and performance in various ways, such as to address changing operational requirements, to correct for bugs (errors in function), or for experimentation.

In the waveform plot on the left in Figure 1-3, a droop or transient reduction is seen in the operating supply, presumably due to an increase in loading, after which the voltage recovers to a nominal value. When the load is released, an overshoot, or transient rise, bigger than the dip is seen, followed by damped oscillations of the supply voltage, before a return to the nominal voltage level. This plot is of a value measured with respect to a ground, and what is observed is a potential

**Figure 1-3** Power supply compression without package capacitors (left) and with package capacitors (right) measured with a 10:1 attenuation probe. Source: Larry Smith and Hong Shi, "Design for Signal & Power Integrity," DesignCon 2007. [6]

difference between power supply nodes. These variations in the power supply potential—the dip, overshoot, and oscillation—are all undesirable in a DC source, and are various forms of power integrity degradation. What is not seen here is the drop in the potential difference with respect to the supplied emf, or the static drop, another aspect of loss of power integrity.

The waveform on the right in Figure 1-3 displays reduction in droop, overshoot, and supply oscillation or ringing, indicating an improvement in power integrity. Whereas signal integrity is often quantified by signal-to-noise ratio (SNR), particularly for analog signals, we know of no equivalent measure of PI. Load and line regulation, which are measures of static variability of supply voltage, are inadequate in describing droops, overshoots, and ringing, all of which contribute to system malfunctions, and are therefore important to quantify. Further chapters will describe efforts made by the industry in this regard.

## 1.4.1 Contributors to PI Degradation

A well-known aspect of PI degradation is the drop in voltage with load current, commonly referred to as *IR drop* in the integrated circuit industry. This is related to a *source resistance* definition for regulated DC power supplies:

Source Resistance =

$$\frac{V_{No \ Load} - V_{Full \ Load}}{I_{Full \ Load}}$$

(1-15)

Source resistance (as its name suggests) relates voltage difference to current and therefore has units of resistance, which relates well to unregulated voltage sources with finite source resistance. The lower this source resistance, the higher the ability of the source to provide power to a load. The lower the source impedance of a regulated power supply, the better the quality of the supply in general.

Source resistance is a property of a power source that contributes to voltage reduction, and is controlled in the design of voltage regulators. Resistance to current flow in the power delivery path (or, more aptly, potential difference transfer path) leads to a reduction in the potential difference as determined by Ohm's Law. This reduction is a dominant component of overall voltage drop and is thoroughly investigated during IC design.

Another key contributor to PI degradation is electromagnetic induction—emf induced in any conductor with changing magnetic flux around it—discovered by Michael Faraday, and independently by Joseph Henry, in 1931:

$$v = L \cdot \frac{di}{dt} \tag{1-16}$$

where *L* is termed inductance. The SI unit of inductance is the *henry*, defined as a *weber* per *ampere*, where the weber is the unit for magnetic flux. An emf thus develops across an inductor when the current flowing through it changes in time. This emf essentially opposes the change in current, just as there is opposition to a change of state in any system (Newton's third law of motion, *"To every action, there is an equal and opposite reaction"*).

It is instructive to revisit the force-voltage analogy to gain an intuitive understanding of inductance and the emf developed across it as given by equation (1-16). Newton's second law of motion is quantified as:

$$F = m \cdot a$$

$$F = m \cdot \frac{dv}{dt}$$

(1-17)

where *F* is force applied, *m* is the mass of the object, and *a* is acceleration, dv/dt, or the rate of change of physical velocity.

One can appreciate the close congruence between Equations (1-16) and (1-17) in a force-voltage analogy, where force in mechanical dynamics is equated with voltage or emf in electrodynamics. As with Equations (1-3) and

(1-4), electric current (or the rate of flow of charge) is equivalent to physical velocity. Inductance L is equivalent to mass m, a property that determines inertia. True to this understanding, inductance L is found to be a property that determines electrical inertia. Electrical inertia is the tendency of a conductor to maintain a flow of charge through it unchanged, or to oppose any change in the rate of flow of charge.

As current flow changes through any power delivery path, by load application or release, substantial transient voltage changes are observed proportional to inductance in the path of charge flow. These voltage changes last at least for durations of change of current. Such voltage variations, or  $L \cdot di/dt$  noise, can degrade PI.  $L \cdot di/dt$  noise may manifest visually as electric sparks that jump across switches in circuits with large inductive loads or conducting large currents.

A third aspect of PI degradation relates to interactions between inductance and capacitance in power delivery pathways. Capacitors, as charge storage elements, are capable of maintaining required potential difference during transient events such as changes in charge flow. They are extensively employed in power delivery to maintain PI. Nevertheless, in combination with path and parasitic inductors, capacitors form what are called "tank" circuits, which create an oscillatory flow of charges when stimulated:

$$f = \frac{1}{2\pi\sqrt{LC}} \tag{1-18}$$

where L is inductance, C is capacitance, and f is called the resonant frequency of the tank circuit formed.

Resonance is a phenomenon where energy is transferred back and forth from potential to kinetic form. In electrical circuits, capacitors and inductors interact in this manner at their resonant frequencies. As discussed in later chapters, resonances are unavoidable in most power delivery systems, often leading to excessive "ringing" of supply voltage. This is seen in Figure 1-3, where package inductance and die capacitance resonate on stimulation by load currents. Resonant behavior degrades PI and consequently signal integrity (SI). In large integrated circuits, or in printed circuit board power delivery planes, two-dimensional voltage resonances and standing wave patterns may also manifest, leading to spatially distributed noise maxima and minima.

These contributors to PI and SI degradation have been referred to by the authors, for easier recollection, as the *3 Rs of interconnect:* resistance, reactance,

#### Exercises

and resonance. Subsequent chapters deal in greater detail with each of these aspects of PI and their combined effects on functionality, performance, and power integrity. We will also discuss methods of analysis, and management through good design practices and advanced techniques.

#### 1.5 Exercises

#### Exercise 1-1

The complement to voltage developed across an inductor due to the flow of electric current is the voltage developed across a capacitor, given as:

$$V = \frac{1}{C} \int_0^t i(t) \cdot dt$$

Describe a mechanical (fluid-based) analogy for this electrical phenomenon.

#### Exercise 1-2

What is the electrical equivalent to Newton's second law of motion,

$$F = m \cdot a$$

$$F = m \cdot \frac{dv}{dt}$$

in the force-current analogy?

#### **Exercise 1-3**

An ideal capacitor of value 2 farads is charged to a voltage of 1V. An ideal inductor of value 2 henry is then instantaneously shorted across the capacitor terminals to form an LC tank circuit.

- a. Describe variations in voltage and current in the circuit formed.

- b. Calculate the peak current value that will flow through this ideal circuit.

It was stated in Section 1.4.1 that resonance leads to supply voltage "ringing," or periodic variation in the power supply differential voltage. Why does supply voltage drop below the nominal value despite the fact that no power is consumed in the reactive components that cause this ringing?

#### **Exercise 1-4**

At nanoscale levels, current in a conductor is the flow of electrons propelled by an electric field that is created by the potential difference across the ends of the conductor. Each electron experiences a force corresponding to its charge, q, and the applied electric field in the conductor material.

What can be a principal phenomenon within the conductor structure at nanoscale levels that limits flow of electric current? What is the physical by-product of this phenomenon in the conductor? Why is this by-product quadratically related to the number of electrons passing through in a unit duration of time?

#### References

- Cheever, E. 2005. Analogous Electrical and Mechanical Systems. Swarthmore College, www.swarthmore.edu/NatSci/echeeve1/Ref/LPSA/Analogs/ ElectricalMechanicalAnalogs.html.

- Wikipedia, The Free Encyclopedia. 2009. http://en.wikipedia.org/wiki/ Main\_Page, various information pages.

- **3.** Kreyszig, E. 1991. *Advanced engineering mathematics*, 5th ed. New York: Wiley.

- **4.** Wikimedia Commons. 2009. http://commons.wikimedia.org/wiki/ Main\_Page, online database of freely usable media files.

- Nair, R., and B. Tang. 1998. Low cost on-die CMOS distributed voltage regulation for microcontrollers. Proceedings of the 24th European Solid-State Circuits Conference (ESSCIRC), September, pp. 188–191.

- **6.** Smith, L. D., and H. Shi. 2007. *Design for signal and power integrity*, DesignCon 2007.

# NDEX

2.5D multilayered FD modeling methodology, 169 2.5D TEM approximations modeling methodology, 164, 166-169 restrictions, 214 2D transmission line modeling methodology, 164 restrictions, 214 2T (two-terminal) chip capacitors, 334-335 3D full-wave modeling case study, 166-169 description, 164-165 restrictions, 214 simulation speed, 169 3D quasi-static modeling methodology, 163, 169 restrictions, 214 3D RC extraction modeling methodology, 163 restrictions, 214 3D RE modeling methodology, 169 3D resistance extraction modeling methodology, 163 restrictions, 214 3D RL modeling methodology, 169 3D RLC extraction description, 163 restrictions, 214 simulation speed, 169 3DICs (3D integrated circuits), 364-365

3Rs of interconnect, 16–17 4004 chip, 20–21

# Α

Abstracting chip components. See also Analyzing PI; Modeling; Simulation. circuit blocks, abstraction, 122-124 decoupling capacitance, abstraction, 122 - 124examples, 129-135 extra-chip interconnects, 124-126 front-end simulation, system-level, 133-135 FUB (functional-block) power grid nets, 121 - 122global chip power grids, 120-122 grid wire inductance, 120-121 limitations, 125 model accuracy, 125 on-chip power grid abstraction, 120-122 on-chip power network design, 132-133 overview, 118-120 power bus pairs, 120 power grid noise distribution, 129-131 system-level characteristics, 124-126, 131 system-level front-end simulation, 133-135 voltage domains, 120 voltage droop vs. ground bounce, 125 AC (alternating current) converting to DC, 8, 9-11 definition. 7-8

AC (alternating current) (contd.) in personal computers, 9 POL (point-of-load) conversion, 10-11 Active impedance modulation, 60 Active noise reduction, 60, 335-341 Active packaging, 335-341 Activity factor, 44-45, 77 Adaptive capacitor placement, 92-94 Adaptive meshing process, 178-179 Adaptive voltage scaling, 11, 114–115, 307 Amperes, 5-6 Analog circuits, low-power chip-level integration, 351 Analyzing PI. See also Abstracting chip components; Modeling; Simulation. dynamic timing analysis, 136 electromagnetic interference. See EMI (electromagnetic interference), analyzing. electromigration hot spots, determining, 115 front end, 118, 133-135 gaps, 117-118 IR drop analysis, 115–117 voltage droop, determining, 117 ANRs (active noise regulators), 336, 338-341 Architectural techniques for PI management, 331 Array capacitors, 334-335 Articles. See Books and publications. Asymmetric variability specifications, 115 Asymmetrical, differential power grids, 72

#### В

Back-gate biasing, 350–351

Ballasting effect, 330–331

Bandgap voltage reference, 65–68

Base-delay causality, 184–186

Batteries, source of electrical power, 1, 7

BBUL (bump-less build-up layer) technology, 355

Binary transfer resistors, 27

Body biasing, 305, 350–351

Body effect, 36

Boltzmann, Ludwig, 36

Boltzmann constant, 36

Books and publications *The Coal Question*, 111 "Cramming More Components into Integrated Circuits," 20

Boost power conversion, 60–64

Brown, William C., 8

Buck power conversion, 60–64

Buck regulators. *See* VRMs (voltage regulator modules).

Buck-boost power conversion, 60–61

Bulk capacitors, 332

Bus inductance, noise, 75

Buses, modeling on-chip switching current, 239–245 skewing, 248–250 verifying, 245–248

# С

Capacitance decoupling. See Decoupling capacitance. effects on power integrity, 45 estimating, 162 PI management, 318-319 Capacitance, system-level noise effects activity factor, 77 charge consumption, 78 charge redistribution, 78 charge sufficiency, 77-78 differential connectivity, 77 FPGA (field-programmable gate array), 78 - 80frequency simulation, 78-80 frequency-domain simulation, 78-80 high-bandwidth, on-die capacitance, 78-79 lumped models, 78–79 spatial distribution, 77 SPICE (Simulation Program with Integrated Circuit Emphasis), 80 time-domain simulation, 78-80 ULSI components, 76-80 voltage droop, 78 Capacitance placement current slope, 85-88 noise dependency, 83-89 Capacitive loads, switching, 25 Capacitors adaptive placement, 92-94 charge multiplication, 336-337

#### Index

charging, 28-34 decoupling. See Decoupling capacitance. energy multiplication, 336-337 storing potential electrical energy, 3-4 uniform placement, 92-94 Capacitors, PI management 2T (two-terminal) chip capacitors, 334-335 active noise reduction, 335-341 active packaging, 335-341 ANRs (active noise regulators), 336, 338 - 341array capacitors, 334-335 bulk capacitors, 332 charge flow for noise reduction, 337 charge multiplication, 336-337 embedded capacitors, 334-335 energy multiplication, 336-337 high bandwidth local regulation, 337-338 IDC capacitors, 334-335 low-inductance capacitors, 335 Carbon nanotubes (CNTs), 351 Central power delivery in personal computers, 9 Central voltage reference generation, 59 Channel length, decoupling capacitance, 321-323 Charge consumption, system-level noise effects. 78 decoupling capacitance, 328-330 flow for noise reduction, 337 multiplication, capacitors, 336-337 redistribution, system-level noise effects. 78 sharing, 35 sufficiency, system-level noise effects, 77-78 Charging a capacitor, 28-34 Chip-level integration. See Integration, chip-level. Chip-level PI degradation, 44 Chip-level PI management. See also Packagelevel PI management; System-level PI management. advanced techniques, 330-331 architecture techniques, 331 ballasting effect, 330-331 capacitance, 318-319

circuit techniques, 331 inductance, 318 leakage, 330-331 primary techniques, 318-319 resistance, 318 Chip-level PI management, decoupling capacitance channel length, 321-323 charge and energy, 328-330 voltage dependency, 326-330 Chip-level PI management, noise impact of well structure, 323-326 measurement and modeling, 319-326 Chips. See ICs (integrated circuits). Circuit blocks, abstracting, 122–124 Circuit simulation programs, 259–260 Circuit techniques for PI management, 331 Circuit-based simulators, 178 Clock gating, 302-303 Closed-form analytical methods, 177–178 Closed-loop power transfer, 68-72 CMOS circuits, power and energy consumption. See also ICs (integrated circuits). body effect, 36 Boltzmann constant, 36 charge sharing, 35 charging a capacitor, 28-34 DIBL (drain-induced barrier lowering), 36 doping, 38 gate oxide tunneling current, 38 goals of, 29 halo pockets, 38 inductance, and signal settling time, 32-34 interconnect capacitance, 35 Kirchhoff's law, 30 Miller effect, 35 RBB (reverse-body bias), 38 short-circuit current, 34 signal ramp time, effects on speed, 32-34 source/drain extensions, 38 sources of, 28-39 spring analogy, 31 subthreshold conduction, 35-39 transition times, optimizing, 32 tunneling currents, 35-39 velocity saturation, 29

CNTs (carbon nanotubes), 351 The Coal Ouestion, 111 Common-mode noise, 69, 230–233 Complementary-to-absolute temperature (CTAT) voltage, 65-66 Conducted/radiated EMI analysis, 211-215 Conductive coupling, 8 Constant-area scaling, 47-48 Constant-field scaling description, 23-24 disadvantages, 26 loop inductance, 47-48 noise, 75 resistance scaling, 48 Constant-voltage scaling, 23, 26, 48 Continuum modeling. See ECD (effective current density), continuum modeling. Continuum models for power grids, 128-129 Converters, 8 Cores, 19-20 Cost issues chip design, 289 PDNs (power delivery networks), 145 per transistor, trends, 21 Coulomb, 1-2 Coupling, and noise, 70-71 "Cramming More Components into Integrated Circuits," 20 Critical net crossing gaps/slots/splits rule, 203-204 Cross-coupling characteristics, 180–182 Cross-over frequency, noise, 74 Crosstalk, and power integrity degradation, 141 - 142Crowbar current, 34, 292-293 CTAT (complementary-to-absolute temperature) voltage, 65-66 Current slope and capacitance placement, 85-88 vs. noise amplitude, 84-85

#### D

Damped resonant response, 43 DC (direct current) converting to AC, 8 definition, 8

in personal computers, 9-11 power integrity, 13 voltage regulation, 12-13 DC extrapolation challenge, 186-188 DC-DC converters boosting output voltage, 12-13 linear, 55-56 power supply efficiency, 55, 60-64 switched, 12-13 Debye modeling, 186 Decap size and position, 85 Decoupling capacitance abstracting, 122-124 designing ICs, 297-300 ESL (equivalent series inductance), 150 - 151ESR (equivalent series resistance), 150-151 frequency domain, 88-89 modeling for noise mitigation, 150-153 noise suppression, 85 on-board, 150, 152 on-chip, 150, 152-153 on-package, 150, 152-153 power grid analysis, 90-94 Decoupling devices, 12 Decoupling optimization, system-level, 193-195 DeltaFET architecture, 349 Design rule conformance (DRC) checker, 196 Designing chip layout. See Floorplanning. power grids, 294-297 Designing ICs, PI considerations crowbar current, minimizing, 292-293 decoupling capacitance, 297-300 discontinuities, resolving, 296-297 dynamic voltage drop analysis, 297-300 electron wind, 296 leakage, minimizing, 292-294 long-term reliability, 296 Moore's Law, 291-292 PI validation, 295–297 power consumption management, 291-294 power grid design, 294-297 static IR drop checker, 295-297 voltage-drop checker, 295-297

#### Index

Designing PDNs. See also Numerical modeling, PDNs. on-board decoupling capacitors, 156-157 on-chip decoupling capacitors, 158-159 on-package decoupling capacitors, 158 reducing inductance, 154-156 Device degradation, 26 DIBL (drain-induced barrier lowering), 36 Dicing, 354 Die-level optimization, 205, 208-211 Differential, low voltage signaling, 71 Differential connectivity, 77 Differential modeling methodology, 169-170, 173-176 Differential pair length matching rule, 204-208 Differential pair return path rule, 204-208 Differential power pathway design, 69 Differential power supply, 71 Differential-mode noise, 230-233 Direct current (DC). See DC (direct current). Discontinuities, resolving, 296–297 Distributed voltage regulation, 59 Distribution networks, 11–12 Distribution of power consumption, 89-94 Djordjevic-Sarkar model, 186 Doping, 38 Dot-statements, 126–128 Double-gate MOSFET, 348-350 DRC (design rule conformance) checker, 196 Droop. See Voltage droop. Dynamic modulation of impedance, 340 Dynamic timing analysis, 136 Dynamic voltage drop, 75, 297–300 Dynamic voltage scaling, 11, 114-115, 307

## Ε

ECD (effective current density) circuit simulation programs, 259–260 definition, 260–262, 371–372 model simplification, 259–260 network symmetry, 263–264 virtual currents, 263 ECD (effective current density), continuum modeling example, 269–273

for IC floorplanning, 273-280 model derivation, 372-382 for nanoscale CMOS circuits, 284 overview, 264-269 vs. SPICE modeling, 280-284 Edison, Thomas, 10 Eigen mode analysis, 193 Electric batteries. See Batteries. Electrical charge, unit of measure, 2 Electrical energy. See also Energy. converting to mechanical, 27 potential, stored in a capacitor, 3-4 Electrical potential difference, expression for. 2 Electrical power. See also PI (power integrity); Power delivery. amperes, 5-6 definition, 5 in electrical systems, 7-8 in electronic systems, 8 forms of. See AC (alternating current); DC (direct current). physical analogy, 6-8 power factor, 6 unit of measure, 5-6 watts, 6 Electrical power, sources of batteries. 1.7 electrochemistry, 7 electromagnetic induction, 7 heat. 7 photovoltaic conversion, 7 piezo-electricity, 7 static electricity, 6-7 sunlight, 7 thermo-electricity, 7 Electrical systems vs. electronic systems, 7-8 Electrochemical sources of electrical power. 7 Electromagnetic coupling, 8 Electromagnetic fields. See also EMI (electromagnetic interference). power supply efficiency, 69-70 source of electrical power, 7 Electromagnetic inductance, power integrity degradation, 15

Electromagnetic solvers, 179 Electromigration hot spots, determining, 115 Electromotive force. See emf (electromotive force). Electron wind, 296 Electronic systems converting electrical energy to mechanical, 27 effects of ULSL 27 effects of ULSI devices, 27 vs. electrical systems, 8 MEMS (micro-electro-mechanical systems), 27 Rayleigh Waves, 27 surface acoustic waves, 27 Electrostatic analysis, 160-161 Embedded capacitors, 334-335 EMC (electromagnetic compatibility), 188-189 emf (electromotive force) discovery of, 1 force-current analogy, 4 force-voltage analogy, 2-4, 15-16 Ohm's Law, 4 units of measure, 1-2 EMI (electromagnetic interference), analyzing. See also Modeling EMI. DRC (design rule conformance) checker, 196 Eigen mode analysis, 193 EMC (electromagnetic compatibility), 188-189 inductance, minimizing, 192 loop area, 194-195 loop resistance, minimizing, 192 overview, 188-189 package resonance, 193 plane resonances, 193 return reference plane discontinuity, 195-197 SSO/SSN high-current transients, 190–192 strengths and weaknesses, 197-198 system-level decoupling optimization, 193-195 system-level rail noise, 190-192 EMI/DRC methodology, 201-205

Energy. See also Electrical energy. decoupling capacitance, 328–330 stored in a magnetic coil, expression for, 3 unit of measure, 1 Energy multiplication, capacitors, 336–337 Energy-delay product metrics, 24, 27 Error analysis, power supply noise, 233–239 ESL (equivalent series inductance), 150–151 ESR (equivalent series resistance), 150–151 eWLB process, 358–359 Extra-chip interconnects, 124–126 Extraction phase, EMI modeling, 200–205 Eye diagrams, 141–142

# F

Fan-in approaches, 355 Fan-out approaches, 355 Faraday, Michael, 15 Faraday's law, 160 FCBGA packages, 361 FD (finite difference) modeling techniques, 173 FDFD (finite difference frequency domain) modeling, 173-176 FDTD (finite difference time domain) modeling, 173-176 FEMs (finite element methods) modeling, 173 Filters AC-DC conversion, 8 electrical power delivery, 12 in personal computers, 12 Fine-pitch BGA packages, 361 FinFET architecture, 349, 350-351 Floorplanning. See also Designing ICs. decoupling capacitance, 297-300 front-end PI analysis, 118 modeling, 273-280 Floorplanning, nanometer-era ICs die cost, 289 performance, 290 power minimization, 290 signal integrity, 291 system requirements, 288-289 Flyback switching, 64 Force, unit of measure, 2 Force-current analogy, 4

#### Index

Force-voltage analogy, 2–4, 15–16 4004 chip, 20–21 FPGAs (field-programmable gate arrays) power integrity, 13–14 system-level noise effects, 78–80 Freescale, 355–356, 357 Frequency sweep challenge, 186–188 Frequency-domain simulation, 78–80 Front-end PI analysis, 118, 133–135 Front-end simulation, system-level, 133–135 FUB (functional-block) power grid nets, 121–122

## G

Galvanic current. *See* DC (direct current). Gate overlap, 349 Gate oxide tunneling current, 38 Gate-oxide integrity, 349 Gauss's law, 160–161 Global chip power grids, 120–122 Green's function, 172–173 Grid pitch, 94–97 Grid wire inductance, 120–121 Ground bounce. *See* Power supply noise. Ground planes, power supply efficiency, 69 Ground potential, power supply efficiency, 69 Ground terminals, 68 Ground wire spacing, noise, 98–99

#### Η

Halo pockets, 38 Headroom. See Margin for error. Heat, source of electrical power, 7 Heat generation, ULSI devices, 39 Helmholtz equation for planar circuits, 383-384 henry (unit of measure), 15 Henry, Joseph, 15 High-bandwidth linear regulators, 57-60 local regulation, 337-338 on-die capacitance, 78-79 Hilbert transform, 186 Holistic integration, 63-64, 366-367 Hooke's Law, 3 Hot carriers, 26 Hybrid solvers, 179

# I

ICs (integrated circuits). See also CMOS circuits: Transistors. cores, 19-20 cost per transistor, trends, 21 definition. 19 MIPS (millions of instructions per second), trends, 21 power consumption, 21 ICs (integrated circuits), Intel Corporation 4004, 20 - 21power consumption trends, 21 Silicon Sandwich architecture, 64 Tanglewood, 19 Tukwila, 19 ICs (integrated circuits), power supply efficiency active impedance modulation, 60 active noise regulation, 60 asymmetrical, differential power grids, 72 bandgap voltage reference, 65-68 boost power conversion, 60-64 buck power conversion, 60-64 buck-boost power conversion, 60-61 central voltage reference generation, 59 common-mode noise, 69 CTAT (complementary-to-absolute temperature) voltage, 65-66 differential, low voltage signaling, 71 differential power pathway design, 69 differential power supply, 71 distributed voltage regulation, 59 dynamic modulation of impedance, 340 electromagnetic fields, 69-70 flyback switching, 64 ground bounce, 70-71 ground planes, 69 ground potential, 69 high-bandwidth linear regulators, 57-60 inverted flyback switching, 64 linear DC-DC converters, 55–56 linear regulators, 56-57 loop inductance scaling relationship, 63 loops, 69 noise, total power integrity, 72-80 noise coupling, 70-71

ICs (integrated circuits), power supply efficiency (contd.) open-drain signaling, 71 power grid impedance, 60 PTAT (proportional-to-absolute temperature) voltage, 65-68 pulse-frequency modulation, 64 pulse-width modulation, 64 reduced-swing transfer gate, 64 resonant operation, 64 single-supply signaling, one wire, 71 skin effect, 70 supply noise, and closed-loop power transfer, 68 - 72switching DC-DC converters, 55, 60-64 symmetrical, differential power grids, 71 temperature-independent voltage, scaling, 65 unipolar (single) power supplies, 70-72 voltage references, 65-68 zener breakdown voltage, 58 Zener diodes, 65 zero potential, zero impedance termination, 69 zero-voltage switching, 64 IDC capacitors, 334-335 Impedance active impedance modulation, 60 dynamic modulation, 340 matching, 332-333 power delivery path impedance, 332-334 power grid impedance, 60 power supply characteristics, 182-184 target, 146-147 zero potential, zero impedance termination, 69 Zin impedance, and target impedance, 147-150 Inductance and di/dt. 74-76 estimating, 162 grid wires, 120-121 minimizing, 192 on-chip. See On-chip inductance, and grid design. parasitic, 143-146 PI management, 318 power/ground network analysis. See On-chip inductance, and grid design.

reducing, 144-145, 154-156 and signal settling time, 32-34 unit of measure, 15 Inductance/capacitance interactions, 16 Inductive drop, noise, 72 iNEMI (International Electronics Manufacturing Initiative), 356 Infineon, 355-356, 358 Integral modeling methodology, 169–173 Integrated circuits (ICs). See ICs (integrated circuits). Integrated electrical power delivery, 11 Integration challenges, 365-366 holistic, 366-367 package-level, 352-353 trends, 366-367 Integration, chip-level back-gate biasing, 350-351 body biasing, 350-351 CNTs (carbon nanotubes), 351 DeltaFET architecture, 349 device architecture, low-power systems, 348-350 double-gate MOSFET, 348-350 FinFET architecture, 349, 350-351 gate overlap, 349 gate-oxide integrity, 349 leakage current, 349 low-power analog circuits, 351 MIGFET architecture, 350 misalignment, 349 multi-gate transistor devices, 349 OmegaFET architecture, 349 problems, 349 signal-to-noise ratio, 350-351 SRAM (static random access memory), 350-351 Tri-Gate architecture, 349 Integration, wafer-level 3DICs (3D integrated circuits), 364–365 BBUL (bump-less build-up layer) technology, 355 dicing, 354 eWLB process, 358-359 fan-in approaches, 355

#### Index

fan-out approaches, 355 FCBGA packages, 361 fine-pitch BGA packages, 361 JEDEC standards, 361 known good die setup, 361 miniaturization, 358-359 Molded Reconfigured Wafer technology, 355 overview, 354-356 package thickness, reducing, 358-359 PoP (package-on-package) technology, 360-362 RCP (Redistributable Package Technology), 355-356, 357 SiP (system-in-package) technology, 356-359 stacked-die packages, 359-360 TSVs (through-silicon-VIAs), 362-365 via first process, 363 via last process, 363 warpage issues, 362 Intel Corporation ICs 4004, 20-21 power consumption trends, 21 Silicon Sandwich architecture, 64 Tanglewood, 19 Tukwila, 19 Interconnect capacitance, 35 Interconnect lines, calculating resistance, 72-74 Interconnects, extra-chip, 124-126 International Electronics Manufacturing Initiative (iNEMI), 356 Inverted flyback switching, 64 Inverters, 8 IR drop analysis, 115-117 power integrity degradation, 14-15 Irregular power distribution grids, 224 ITRS (International Technology Roadmap for Semiconductors), 356

## J

Jacobi, Hermann von, 54–55 Jacobi's Law, 54–55 JEDEC standards, 361 Jevons, Walter Stanley, 111 Jevons Paradox, 111 Joules, 1–2 Joules per coulomb, 1–2 Journal articles. *See* Books and publications.

#### Κ

Kinetic energy, expression for, 3 Kirchhoff, Gustav, 30 Kirchhoff's law, 30 K-K (Kramers-Kronig) relationship, 186 Known good die setup, 361

## L

Large-scale integration (LSI), 19 Layout creation phase, EMI modeling, 200-205 Leakage body effect, 36 Boltzmann constant, 36 constant-field scaling, 37 DIBL (drain-induced barrier lowering), 36 doping, 38 effects of higher speeds, 29 FET leakage currents, 35-39 gate oxide tunneling current, 38 halo pockets, 38 junction leakage currents, 38 minimizing, 292-294 PI management, 330-331 RBB (reverse-body bias), 38 source/drain extensions, 38 subthreshold conduction, 35, 37 total leakage current, 38-39 tunneling, 35 Leakage current, chip-level integration, 349 Linear DC-DC converters, 55–56. See also DC-DC converters. Linear regulation, electrical power delivery, 12 - 13Linear regulators, power supply efficiency, 56-57 Lithography capability, 22 Load circuits, noise, 69-70 Load regulation, electrical power delivery, 12 - 13Loop area, 194–195

Loop inductance scaling, 44–48, 63 Loop resistance, minimizing, 192 Loops, power supply efficiency, 69 Low-inductance capacitors, 335 Low-power analog circuits, 351 LSI (large-scale integration), 19 Lumped models, system-level noise effects, 78–79

#### Μ

Magnetic flux, unit of measure, 15 Magnetic monopoles, 160-161 Margin for error, noise, 70, 72 Maxwell, James Clerk, 2 Maxwell's equations, 160-161 MEMS (micro-electro-mechanical systems), 27 Method of moments (MoM), 170-176. See also PEEC (partial element equivalent circuit). MFDM (multilayered finite difference method) modeling methodology, 174–176 Microchips circuits. See ICs (integrated circuits). Microelectronic circuits. See ICs (integrated circuits). Micrometer to nanometer scaling, 23-24 **MIGFET** architecture. 350 Miller, John Milton, 35 Miller effect, 35 Miniaturization, 358-359 MIPS (millions of instructions per second), trends, 21 Misalignment, chip-level integration, 349 Model abstraction phase, EMI modeling, 200 - 205Model simplification, 259-260 Modeling decoupling capacitors, for noise mitigation, 150 - 153ECD (effective current density). See ECD (effective current density), continuum modeling. MoM (method of moments) modeling methodology, 170-176 noise, 150-153, 319-326 numerical methodologies. See Numerical modeling methodologies.

power distribution grids, 224-229. See also Numerical analysis, power distribution models. power supply noise. See Power supply noise, modeling. voltage drop across edges, 172-173 Modeling EMI. See also EMI (electromagnetic interference), analyzing. best practices, 200-205 conducted/radiated EMI analysis, 211-215 critical net crossing gaps/slots/splits rule, 203 - 204die-level optimization, 205, 208-211 differential pair length matching rule, 204 - 208differential pair return path rule, 204-208 EMI/DRC methodology, 201-205 extraction phase, 200-205 layout creation phase, 200-205 model abstraction phase, 200-205 overview, 198 phases, summary of, 199-200. See also specific phases. simulation methods, restrictions, 214 Modeling EMI, rules. See also specific rules. checking, 202 definition. 201 preparation, 201 testing, 202 Molded Reconfigured Wafer technology, 355 MoM (method of moments), 170–176. See also PEEC (partial element equivalent circuit). Moore, Gordon, 20-21, 291 Moore's Law, 21, 291–292 MOSFET devices, illustrations, 22, 36. See also Transistor scaling, MOSFET devices. Motherboards (illustration), 9-10 MSI (medium-scale integration), 19 Multi-gate transistor devices, 349 Multilayered finite difference method (MFDM) modeling methodology, 174-176 Multi-V, libraries, 303–304

#### Ν

Nanoscale CMOS circuits, modeling, 284 Negative supply terminal, 68–69

#### Index