# Model-Based Engineering with AADL

An Introduction to the SAE Architecture Analysis and Design Language

#### Peter H. Feiler

# David P. Gluch

#### FREE SAMPLE CHAPTER

# Model-Based Engineering with AADL

Visit informit.com/sei for a complete list of available products.

The SEI Series in Software Engineering represents is a collaborative undertaking of the Carnegie Mellon Software Engineering Institute (SEI) and Addison-Wesley to develop and publish books on software engineering and related topics. The common goal of the SEI and Addison-Wesley is to provide the most current information on these topics in a form that is easily usable by practitioners and students.

Books in the series describe frameworks, tools, methods, and technologies designed to help organizations, teams, and individuals improve their technical or management capabilities. Some books describe processes and practices for developing higher-quality software, acquiring programs for complex systems, or delivering services more effectively. Other books focus on software and system architecture and product-line development. Still others, from the SEI's CERT Program, describe technologies and practices needed to manage software and network security risk. These and all books in the series address critical problems in software engineering for which practical solutions are available.

#### PEARSON

# Model-Based Engineering with AADL

An Introduction to the SAE Architecture Analysis & Design Language

Peter H. Feiler David P. Gluch

✦Addison-Wesley

Upper Saddle River, NJ • Boston • Indianapolis • San Francisco New York • Toronto • Montreal • London • Munich • Paris • Madrid Capetown • Sydney • Tokyo • Singapore • Mexico City

# Software Engineering Institute | Carnegie Mellon

#### The SEI Series in Software Engineering

Many of the designations used by manufacturers and sellers to distinguish their products are claimed as trademarks. Where those designations appear in this book, and the publisher was aware of a trademark claim, the designations have been printed with initial capital letters or in all capitals.

CMM, CMMI, Capability Maturity Model, Capability Maturity Modeling, Carnegie Mellon, CERT, and CERT Coordination Center are registered in the U.S. Patent and Trademark Office by Carnegie Mellon University.

ATAM; Architecture Tradeoff Analysis Method; CMM Integration; COTS Usage-Risk Evaluation; CURE; EPIC; Evolutionary Process for Integrating COTS Based Systems; Framework for Software Product Line Practice; IDEAL; Interim Profile; OAR; OCTAVE; Operationally Critical Threat, Asset, and Vulnerability Evaluation; Options Analysis for Reengineering; Personal Software Process; PLTP; Product Line Technical Probe; PSP; SCAMPI; SCAMPI Lead Appraiser; SCAMPI Lead Assessor; SCE; SEI; SEPG; Team Software Process; and TSP are service marks of Carnegie Mellon University.

Special permission to reproduce in this book two figures from Feiler, Peter; Hansson, Jörgen; de Niz, Dionisio; & Wrage, Lutz. System Architecture Virtual Integration: An Industrial Case Study (CMU/ SEI-2009-TR-017), Copyright © 2009 by Carnegie Mellon University; a variant of a figure from an article and conference presentation: Peter H. Feiler, "Model-based Validation of Safety-Critical Embedded Systems," Proceedings of IEEE Aerospace Conference, March 2010; and three figures from the SEI course: "Modeling System Architectures using the Architecture Analysis and Design Language (AADL)" is granted by the Software Engineering Institute.

The authors and publisher have taken care in the preparation of this book, but make no expressed or implied warranty of any kind and assume no responsibility for errors or omissions. No liability is assumed for incidental or consequential damages in connection with or arising out of the use of the information or programs contained herein.

The publisher offers excellent discounts on this book when ordered in quantity for bulk purchases or special sales, which may include electronic versions and/or custom covers and content particular to your business, training goals, marketing focus, and branding interests. For more information, please contact:

U.S. Corporate and Government Sales (800) 382-3419 corpsales@pearsontechgroup.com

For sales outside the United States, please contact:

International Sales international@pearsoned.com

Visit us on the Web: informit.com/aw

Cataloging-in-Publication data is on file with the Library of Congress.

Copyright © 2013 Pearson Education, Inc.

All rights reserved. Printed in the United States of America. This publication is protected by copyright, and permission must be obtained from the publisher prior to any prohibited reproduction, storage in a retrieval system, or transmission in any form or by any means, electronic, mechanical, photocopying, recording, or likewise. To obtain permission to use material from this work, please submit a written request to Pearson Education, Inc., Permissions Department, One Lake Street, Upper Saddle River, New Jersey 07458, or you may fax your request to (201) 236-3290.

ISBN-13: 978-0-321-88894-5 ISBN-10: 0-321-88894-4

Text printed in the United States on recycled paper at Courier in Westford, Massachusetts. First printing, September 2012

# Contents

| Preface                                            | xv |

|----------------------------------------------------|----|

| Introduction                                       | 1  |

| PART I Model-Based Engineering and the AADL        | 3  |

| Chapter 1 Model-Based Software Systems Engineering | 5  |

| 1.1 MBE and Software System Engineering            | 6  |

| 1.1.1 MBE for Embedded Real-Time Systems           | 6  |

| 1.1.2 Analyzable Models and MBE                    | 8  |

| 1.1.3 MBE and the AADL                             | 10 |

| 1.2 AADL and Other Modeling Languages              | 12 |

| 1.2.1 AADL, MDA, and UML                           | 14 |

| 1.2.2 AADL and SysML                               | 15 |

| Chapter 2 Working with the SAE AADL                | 17 |

| 2.1 AADL Models                                    | 19 |

| 2.1.1 Component Categories                         | 19 |

| 2.1.2 Language Syntax                              | 20 |

| 2.1.3 AADL Classifiers                             | 21 |

| 2.1.4 Summary of AADL Declarations                 | 22 |

| 2.1.5 Structure of AADL Models                     | 25 |

| 2.2 System Specification and System Instances      | 26 |

| 2.2.1 Creating System Instance Models              | 26 |

| 2.2.2 AADL Textual and Graphical Representation    | 27 |

| 2.2.3 Analyzing Models                             | 30 |

| Chapter 3 Mo | deling and Analysis with the AADL: The Basics   | 31 |

|--------------|-------------------------------------------------|----|

| 3.1 Dev      | veloping a Simple Model                         | 31 |

| 3.1.1        | Defining Components for a Model                 | 32 |

| 3.1.2        | Developing a Top-Level Model                    | 36 |

|              | Detailing the Control Software                  | 38 |

| 3.1.4        | Adding Hardware Components                      | 40 |

| 3.1.5        | Declaring Physical Connections                  | 41 |

| 3.1.6        | Binding Software to Hardware                    | 43 |

|              | Conducting Scheduling Analyses                  | 45 |

| 3.1.8        | Summary                                         | 47 |

| 3.2 Rep      | presenting Code Artifacts                       | 47 |

| 3.2.1        | Documenting Source Code and Binary Files        | 48 |

| 3.2.2        | Documenting Variable Names                      | 49 |

| 3.2.3        | Modeling the Source Code Structure              | 50 |

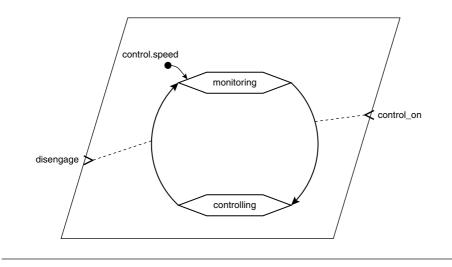

| 3.3 Mo       | deling Dynamic Reconfigurations                 | 51 |

| 3.3.1        | Expanded PBA Model                              | 51 |

| 3.3.2        | Specifying Modes                                | 53 |

| 3.4 Mo       | deling and Analyzing Abstract Flows             | 55 |

| 3.4.1        | Specifying a Flow Model                         | 55 |

| 3.4.2        | Specifying an End-to-End Flow                   | 57 |

| 3.4.3        | Analyzing a Flow                                | 57 |

| 3.5 Dev      | veloping a Conceptual Model                     | 58 |

| 3.5.1        | Employing Abstract Components in a PBA Model    | 58 |

| 3.5.2        | Detailing Abstract Implementations              | 61 |

| 3.5.3        | Transforming into a Runtime Representation      | 63 |

| 3.5.4        | Adding Runtime Properties                       | 65 |

| 3.5.5        | Completing the Specification                    | 67 |

| 3.6 Wo       | rking with Component Patterns                   | 69 |

| 3.6.1        | Component Libraries and Reference Architectures | 69 |

| 3.6.2        | Establishing a Component Library                | 70 |

| 3.6.3        | Defining a Reference Architecture               | 72 |

| 3.6.4        | Utilizing a Reference Architecture              | 74 |

#### Contents

| Chapter 4 Applying AADL Capabilities |                                                              | 77  |

|--------------------------------------|--------------------------------------------------------------|-----|

| 4.1 Spe                              | cifying System Composition                                   | 77  |

| 4.1.1                                | Component Hierarchy                                          | 77  |

| 4.1.2                                | Modeling Execution Platform Resources                        | 78  |

| 4.1.3                                | Execution Platform Support of Communication                  | 80  |

| 4.1.4                                | System Hierarchy                                             | 81  |

| 4.1.5                                | Creating a System Instance Model                             | 81  |

| 4.1.6                                | Working with Connections in System Instance<br>Models        | 82  |

| 4.1.7                                | Working with System Instance Models                          | 83  |

| 4.2 Cor                              | nponent Interactions                                         | 84  |

| 4.2.1                                | Modeling Directional Exchange of Data and Control            | 85  |

| 4.2.2                                | Modeling Shared Data Exchange                                | 86  |

| 4.2.3                                | Modeling Local Service Requests or Function<br>Invocation    | 87  |

| 4.2.4                                | Modeling Remote Service Requests and Function<br>Invocations | 90  |

| 4.2.5                                | Modeling Object-Oriented Method Calls                        | 92  |

| 4.2.6                                | Modeling Subprogram Parameters                               | 95  |

| 4.2.7                                | Interfacing to the External World                            | 97  |

| 4.3 Mo                               | deling Data and Its Use                                      | 97  |

| 4.3.1                                | Defining a Simple Data Type                                  | 98  |

| 4.3.2                                | Representing Variants of a Data Type                         | 99  |

| 4.3.3                                | Detailing a Data Type                                        | 100 |

| C                                    | anizing a Design                                             | 101 |

|                                      | Using Packages                                               | 102 |

|                                      | Developing Alternative Implementations                       | 104 |

| 4.4.3                                | Defining Multiple Extensions                                 | 105 |

| PART II Elements of the AADL                    |     |  |

|-------------------------------------------------|-----|--|

| Chapter 5 Defining AADL Components              |     |  |

| 5.1 Component Names                             | 113 |  |

| 5.2 Component Categories                        | 114 |  |

| 5.3 Declaring Component Types                   | 114 |  |

| 5.4 Declaring a Component's External Interfaces | 118 |  |

| 5.5 Declaring Component Implementations         | 121 |  |

| 5.6 Summary                                     | 125 |  |

| Chapter 6 Software Components                   | 127 |  |

| 6.1 Thread                                      | 128 |  |

| 6.1.1 Representation                            | 130 |  |

| 6.1.2 Properties                                | 131 |  |

| 6.1.3 Constraints                               | 132 |  |

| 6.2 Thread Group                                | 133 |  |

| 6.2.1 Representations                           | 133 |  |

| 6.2.2 Properties                                | 134 |  |

| 6.2.3 Constraints                               | 134 |  |

| 6.3 Process                                     | 135 |  |

| 6.3.1 Representations                           | 136 |  |

| 6.3.2 Properties                                | 137 |  |

| 6.3.3 Constraints                               | 137 |  |

| 6.4 Data                                        | 138 |  |

| 6.4.1 Representations                           | 138 |  |

| 6.4.2 Properties                                | 140 |  |

| 6.4.3 Constraints                               | 140 |  |

| 6.5 Subprogram                                  | 141 |  |

| 6.5.1 Representations                           | 143 |  |

| 6.5.2 Properties                                | 143 |  |

| 6.5.3 Constraints                               | 144 |  |

| 6.6 Subprogram Group                            | 144 |  |

| 6.6.1 Representations                           | 145 |  |

| 6.6.2                                      | Properties                 | 146 |

|--------------------------------------------|----------------------------|-----|

| 6.6.3                                      | Constraints                | 146 |

| Chapter 7 Exe                              | cution Platform Components | 147 |

| 7.1 Pro                                    | cessor                     | 148 |

| 7.1.1                                      | Representations            | 148 |

| 7.1.2                                      | Properties                 | 150 |

| 7.1.3                                      | Constraints                | 150 |

| 7.2 Virt                                   | ual Processor              | 151 |

| 7.2.1                                      | Representations            | 151 |

| 7.2.2                                      | Properties                 | 152 |

| 7.2.3                                      | Constraints                | 152 |

| 7.3 Mei                                    | mory                       | 153 |

| 7.3.1                                      | Representations            | 153 |

| 7.3.2                                      | Properties                 | 154 |

| 7.3.3                                      | Constraints                | 155 |

| 7.4 Bus                                    |                            | 156 |

| 7.4.1                                      | Representations            | 156 |

| 7.4.2                                      | Properties                 | 157 |

| 7.4.3                                      | Constraints                | 157 |

| 7.5 Virt                                   | rual Bus                   | 158 |

| 7.5.1                                      | Representations            | 158 |

| 7.5.2                                      | Properties                 | 159 |

| 7.5.3                                      | Constraints                | 159 |

| 7.6 Dev                                    | vice                       | 160 |

| 7.6.1                                      | Representations            | 160 |

| 7.6.2                                      | Properties                 | 161 |

| 7.6.3                                      | Constraints                | 161 |

| Chapter 8 Composite and Generic Components |                            | 163 |

| 8.1 Sys                                    | tem                        | 163 |

| 8.1.1                                      | Representations            | 164 |

| 8.1.2                                      | Properties                 | 165 |

| 8.1.3                                      | Constraints                | 165 |

| 8.2 Abs                           | stract                                                 | 165 |

|-----------------------------------|--------------------------------------------------------|-----|

| 8.2.1                             | Representations                                        | 166 |

| 8.2.2                             | Properties                                             | 168 |

| 8.2.3                             | Constraints                                            | 168 |

| Chapter 9 Stat                    | tic and Dynamic Architecture                           | 169 |

| 9.1 Sub                           | ocomponents                                            | 169 |

| 9.1.1                             | Declaring Subcomponents                                | 170 |

| 9.1.2                             | Using Subcomponent Declarations                        | 170 |

| 9.1.3                             | Declaring Subcomponents as Arrays                      | 172 |

| 9.2 Mo                            | des                                                    | 173 |

| 9.2.1                             | Declaring Modes and Mode Transitions                   | 174 |

| 9.2.2                             | Declaring Modal Component Types and<br>Implementations | 175 |

| 9.2.3                             | Using Modes for Alternative Component                  |     |

|                                   | Configurations                                         | 177 |

| 9.2.4                             | Inheriting Modes                                       | 180 |

| 9.2.5                             | Mode-Specific Properties                               | 181 |

| 9.2.6                             | Modal Configurations of Call Sequences                 | 182 |

| Chapter 10 Component Interactions |                                                        |     |

| 10.1 Pc                           | orts and Connections                                   | 186 |

| 10.1.1                            | 1 Declaring Ports                                      | 186 |

| 10.1.2                            | 2 Declaring Port to Port Connections                   | 189 |

| 10.1.3                            | 3 Using Port to Port Connections                       | 189 |

| 10.1.4                            | 4 Constraints on Port to Port Connections              | 193 |

| 10.1.5                            | 5 Port Communication Timing                            | 196 |

| 10.1.6                            | 6 Sampled Processing of Data Streams                   | 198 |

| 10.1.2                            | 7 Deterministic Sampling                               | 199 |

| 10.1.8                            | 8 Mixed Port-Based and Shared Data                     |     |

|                                   | Communication                                          | 203 |

| 10.1.9                            | 9 Port and Port Connection Properties                  | 207 |

| 10.1.1                            | 10 Aggregate Data Communication                        | 207 |

| 10.2 Dat       | a Access and Connections                                   | 210 |

|----------------|------------------------------------------------------------|-----|

| 10.3 Bus       | Access and Connections                                     | 213 |

| 10.4 Fea       | ture Groups and Connections                                | 217 |

| 10.4.1         | Declaring Feature Group Types                              | 218 |

| 10.4.2         | Declaring a Feature Group as a Feature of a Component      | 220 |

| 10.4.3         | Declaring Feature Group Connections                        | 221 |

| 10.5 Abs       | stract Features and Connections                            | 225 |

| 10.5.1         | Declaring Abstract Features                                | 226 |

| 10.5.2         | Refining Abstract Features                                 | 226 |

| 10.6 Arr       | ays and Connections                                        | 227 |

| 10.6.1         | Explicitly Specified Array Connections                     | 228 |

| 10.6.2         | Array Connection Patterns                                  | 229 |

| 10.6.3         | Using Array Connection Properties                          | 230 |

| 10.7 Sub       | program Calls, Access, and Instances                       | 232 |

| 10.7.1         | Declaring Calls and Call Sequences                         | 233 |

| 10.7.2         | Declaring Remote Subprogram Calls as<br>Bindings           | 234 |

| 10.7.3         | Declaring Remote Subprogram Calls as<br>Access Connections | 236 |

| 10.7.4         | Modeling Subprogram Instances                              | 237 |

| 10.8 Par       | ameter Connections                                         | 240 |

| 10.8.1         | Declaring Parameters                                       | 240 |

| 10.8.2         | Declaring Parameter Connections                            | 241 |

| Chapter 11 Sys | tem Flows and Software Deployment                          | 245 |

| 11.1 Flow      | WS                                                         | 245 |

| 11.1.1         | Declaring Flow Specifications                              | 246 |

| 11.1.2         | Declaring Flow Implementations                             | 249 |

| 11.1.3         | Declaring End-to-End Flows                                 | 253 |

| 11.1.4         | Working with End-to-End Flows                              | 256 |

| 11.2 Bine      | ding Software to Hardware                                  | 256 |

| 11.2.1         | Declaring Bindings with Properties                         | 257 |

| 11.2.2         | Processor Bindings                                         | 259 |

| 11.2.3 Memory Bindings                               | 259 |

|------------------------------------------------------|-----|

| 11.2.4 Connection Bindings                           | 260 |

| 11.2.5 Binding Remote Subprogram Calls               | 260 |

| Chapter 12 Organizing Models                         | 263 |

| 12.1 Naming and Referencing Model Elements           | 263 |

| 12.1.1 Naming and Referencing with Packages          | 263 |

| 12.1.2 Naming and Referencing Classifiers            | 264 |

| 12.1.3 References to Model Elements                  | 265 |

| 12.1.4 Naming and Referencing with Property Sets     | 266 |

| 12.2 Organizing Models with Packages                 | 266 |

| 12.2.1 Declaring Packages                            | 267 |

| 12.2.2 Referencing Elements in Packages              | 269 |

| 12.2.3 Aliases for Packages and Type References      | 271 |

| 12.3 Evolving Models by Classifier Refinement        | 273 |

| 12.3.1 Declaring Classifier Extensions               | 274 |

| 12.3.2 Declaring Model Element Refinements           | 275 |

| 12.3.3 Classifier Substitution Rules for Refinements | 277 |

| 12.3.4 Refining the Category                         | 280 |

| 12.4 Prototypes as Classifier Parameters             | 281 |

| 12.4.1 Declaring Prototypes                          | 281 |

| 12.4.2 Using Prototypes                              | 283 |

| 12.4.3 Providing Prototype Actuals                   | 284 |

| 12.4.4 Properties                                    | 287 |

| Chapter 13 Annotating Models                         | 289 |

| 13.1 Documenting Model Elements                      | 289 |

| 13.1.1 Comments and Description Properties           | 289 |

| 13.1.2 Empty Component Sections                      | 290 |

| 13.2 Using Properties                                | 291 |

| 13.2.1 Assigning Property Values                     | 292 |

| 13.2.2 AADL Property Types and Values                | 294 |

| 13.2.3 Determining a Property Value                  | 297 |

| 13.2.4 Contained Property Associations            | 299 |

|---------------------------------------------------|-----|

| 13.2.5 Determining the Property Value: An Example | 300 |

| Chapter 14 Extending the Language                 | 303 |

| 14.1 Property Sets                                | 303 |

| 14.1.1 Declaring Property Sets                    | 304 |

| 14.1.2 Property Type Declarations                 | 305 |

| 14.1.3 Property Definitions                       | 309 |

| 14.1.4 Property Constant Declarations             | 311 |

| 14.2 Annex Sublanguages                           | 312 |

| 14.2.1 Declaring Annex Concepts in Libraries      | 313 |

| 14.2.2 Using Annex Concepts in Subclauses         | 314 |

| Chapter 15 Creating and Validating Models         | 317 |

| 15.1 Model Creation                               | 317 |

| 15.2 Model Creation Tools                         | 319 |

| 15.3 System Validation and Generation             | 321 |

| 15.4 System Validation and Generation Tools       | 322 |

| Appendixes                                        | 325 |

| Appendix A Syntax and Property Summary            | 327 |

| A.1 AADL Syntax                                   | 327 |

| A.2 Component Type and Implementation Elements    | 342 |

| A.3 Basic Property Types and Type Constructors    | 347 |

| A.4 AADL Reserved Words                           | 348 |

| A.5 AADL Properties                               | 349 |

| A.5.1 Deployment Properties                       | 350 |

| A.5.2 Thread-Related Properties                   | 364 |

| A.5.3 Timing Properties                           | 371 |

| A.5.4 Communication Properties                    | 384 |

| A.5.5 Memory-Related Properties                   | 391 |

| A.5.6 Programming Properties                      | 398 |

|                                                   |     |

| A.5.7 Modeling Properties                           | 408 |

|-----------------------------------------------------|-----|

| A.5.8 Project-Specific Constants and Property Types | 410 |

| A.6 Runtime Services                                | 418 |

| A.6.1 Application Runtime Services                  | 418 |

| A.6.2 Runtime Executive Services                    | 421 |

| A.7 Powerboat Autopilot System                      | 425 |

| A.7.1 Description                                   | 425 |

| A.7.2 Enhanced Versions of the PBA System           | 426 |

| A.7.3 AADL Components of the PBA System             | 427 |

| A.7.4 An Alternative AADL Representation            | 428 |

| Appendix B Additional Resources                     |     |

| B.1 Modeling System Architectures                   | 429 |

| B.2 Cases Studies                                   | 431 |

| Appendix C References                               | 435 |

| Index                                               | 441 |

# Preface

In this book, we introduce readers to the concepts, structure, and use of the SAE Architecture Analysis & Design Language (AADL) and demonstrate how AADL is an effective tool for Model-Based Engineering (MBE) of software system architectures. If you are just learning about AADL, we provide sufficient detail to enable you to develop and analyze basic system models. The core skills acquired by mastering the material in this book will provide you a foundation upon which to build your AADL and MBE expertise. Even when you are an accomplished AADL user, we anticipate you will find this book to be a valuable reference.

### What and Why: MBE and AADL

Model-based engineering is the creation and analysis of models of your system such that you can predict and understand its capabilities and operational quality attributes (e.g., its performance, reliability, or security). By doing so throughout the lifecycle, you can discover systemlevel problems—those usually not found until system integration and acceptance testing—and avoid costly rework late in development and maintenance. In the past, separate models have been created for various system components and for each of the different analyses. A systematic and less fragmented approach is an architecture-centric one. Architecture-centric approaches address system-level issues and maintain a self-consistent set of analytical views of a system such that individual analyses retain their validity amidst architectural changes within the set.

The Architecture Analysis & Design Language (AADL) is an SAE International (formerly known as the Society of Automotive Engineers) standard [AS5506A<sup>1</sup>]. The AADL is a unifying framework for modelbased software systems engineering that you use to capture the static modular software architecture, the runtime architecture in terms of communicating tasks, the computer platform architecture on which the software is deployed, and any physical system or environment with which the system interacts. You capture both the static structure and the dynamics in a single architecture model and annotate it with information that is relevant to the analysis of various operational characteristics. The concepts provided by AADL, such as threads, processes, or devices, have well-defined execution semantics that allow you to conduct both lightweight and formal analyses of systems. In addition, using its extensibility constructs, you as well as tool developers can blend custom analysis and specification techniques with core AADL capabilities to create a complete engineering environment for architectural modeling and analysis.

In developing an AADL model, you represent the architecture of your system as a hierarchy of interacting components. You organize interface specifications and implementation blueprints of software, hardware, and physical components into packages to support largescale and team-based development.

As a standard, AADL provides you with the stability often not found in propriety technologies and allows you to participate in defining enhancements to the language. Additional elements of the standard suite that extend the AADL framework are found in the *SAE Architecture Analysis and Design Language (AADL) Annex Volume 1* [AS5506/1] and *SAE Architecture Analysis and Design Language (AADL) Annex Volume 2* [AS5506/2]. Released as a standard in June 2006, SAE AS-5506/1 defines annexes for the AADL graphical Notation, AADL Meta-Model and Interchange Formats, Language Compliance and Application Program Interface, and Error Model Language. Released as a standard in January 2011, SAE AS-5506/2 defines annexes for Behavior Modeling, for guidance on incorporating Data Modeling with AADL, and for ARINC653 Partitioned Architecture modeling.<sup>2</sup>

<sup>1.</sup> The standard AS5506A was originally published in November 2004. The book covers its revision published in January 2009, as well as errata corrections approved in 2012. For more information on the AADL, go to the Web site www.aadl.info. To purchase a copy of the standard, go to the Web site www.sae.org/technical/standards/AS5506A.

<sup>2.</sup> Additional annexes are in development for ballot in late 2012: a revision of the Error Model Annex standard, a Requirements Definition and Analysis Annex, and a Code Generation Annex.

# Who Will Benefit from Reading This Book

You benefit from this book if you are a developer of software-reliant systems, whether a system or software architect, a system engineer, or an embedded software system developer. This book provides a foundation to enable you to apply the AADL and model-based engineering directly in your work. If you are a technical leader or project manager, the core principles and examples discussed in this book provide you with the knowledge required to guide technical personnel in the application of the AADL.

For graduate and advanced undergraduate software engineering students, this book offers a basis to understand and apply the AADL and MBE in your learning experiences. This book can be used as part of the material for a course on software architecture or software systems engineering of embedded real-time applications.

# What You Need to Know to Get the Most Value from This Book

A basic knowledge of core software engineering practices (e.g., software architecture, software design), real-time systems (e.g., concurrency, scheduling, communications), and knowledge of computer runtime concepts (e.g., threads, execution semantics) will help you benefit most from this book. As a minimum, the level of expertise you should have in these areas is that commensurate with an advanced undergraduate student in computer science or software engineering. If you are a software developer with a degree in a technical discipline with two to three years' experience in developing embedded real-time software systems, you will find this book especially valuable in modeling software system architectures.

# Structure of the Book

We have organized the material in the book into two parts, plus three appendixes. Part I is an overview of both the AADL language and MBE practices. It presents basic software systems modeling and analysis using the AADL in the context of an example system, including guidelines for effectively applying the AADL. Part II describes the characteristics of the elements of the AADL including representations, applicability, and constraints on their use. The appendixes include comprehensive listings of AADL language elements, properties that are defined as part of the AADL standard, a description of the example system used in the book, a list of references, and an index.

# Terminology

AADL is a component-based modeling language that distinguishes between component interface specifications (component type declarations), component implementation blueprints (component implementation declarations), and component instances (subcomponent declarations). Component types and implementations are referred to as component classifiers. AADL also distinguishes between component categories with specific semantics to model the application software (e.g., thread, process, data), the execution platform (e.g., processor, bus, device), and composite components (system). The AADL standard document uses terms such as *system type declaration* or *system implementation declaration*. In this book, we use abbreviated terms such as *system type* or *system* where the context makes the meaning clear.

# **Example Application System**

We use a powerboat autopilot (PBA) control system as the basis for most of the examples throughout this book. The PBA is an embedded real-time system for the speed, navigational, and guidance control of a maritime vessel. However, the PBA is an invention created to provide a backdrop for demonstrating the AADL and does not represent any specific commercial, military, or research system. While the PBA is a maritime application, it represents key elements of vehicle control for a wide range of applications including aircraft, spacecraft, and automotive and other land vehicles.<sup>3</sup>

<sup>3.</sup> Details of the PBA system are provided in Appendix A.

### About the Authors

**Dr. Peter Feiler** is a Senior Member of Technical Staff in the Research Technology and Systems Solutions (RTSS) program at the Software Engineering Institute (SEI). He is a 27-year veteran of the SEI. His interests include architecture-centric engineering of safety-critical embedded real-time systems. He is collaborating with researchers at Carnegie Mellon University and other research institutions to develop model-based architecture technology and is investigating its practical-ity with commercial industry. He is the author and editor of the SAE International (formerly known as Society of Automotive Engineers) Architecture Analysis & Design Language (AADL) standard. Peter has a Ph.D. in computer science from Carnegie Mellon University and is a senior member and member of ACM, IEEE, and SAE International. He recently received the Carnegie Science Award for Information Technology.

**Dr. David P. Gluch** is a professor in the Department of Electrical, Computer, Software, and Systems Engineering at Embry-Riddle Aeronautical University and a visiting scientist at the Software Engineering Institute (SEI). His research interests are technologies and practices for model-based software engineering of complex systems, with a focus on software verification. Prior to joining the faculty at Embry-Riddle, he was a senior member of the technical staff at the SEI where he participated in the development and transition of innovative software engineering practices and technologies. His industrial research and development experience has included fault-tolerant computer, fly-by-wire aircraft control, Space Shuttle software modeling, and automated process control systems. He has co-authored a book on real-time UNIX systems and authored numerous technical reports and professional articles. Dave has a Ph.D. in physics from Florida State University and is a senior member of IEEE.

# Acknowledgments

We would like to thank a number of people for helping make this book a reality.

We would like to thank Bruce Lewis as the chair of the SAE AADL committee in making AADL a reality. The quarterly standards meetings provided a forum for user feedback on the use of AADL. We would

also like to thank the members of the committee, especially those from industry, in helping to shape AADL into a language that meets a practical need. It was in this setting that the idea for a book on the use of AADL in model-based engineering came about.

We also appreciate the efforts of the research and advanced technology community from various universities and industry in using AADL as a platform for a wide range of formal software-reliant system analysis and demonstrating the feasibility of model-based engineering with AADL. Their tools and technology to drive the analysis of architectures allows AADL to show off its strength.

At the Software Engineering Institute (SEI), we are thankful to Tricia Oberndorf and Linda Northrop, our program managers for allowing us to invest time and effort into the endeavor of writing this book and encouraging us to bring it to completion. The other SEI AADL team members, Lutz Wrage, Aaron Greenhouse, John Hudak, Joseph Seibel, Dio DeNiz, and Craig Meyers, contributed in various form to the body of knowledge on the use of AADL, a small portion of which is reflected in this book. They led and contributed to the creation and use of the OSATE tool set, the development and presentation of tutorials and two courses on AADL, and the use of AADL on customer projects. We also received feedback on various drafts of the book.

We appreciate the feedback from external reviewers of book drafts, in particular Bruce Lewis, Jérôme Hugues, and Oleg Sokolsky. Finally, we want to thank Peter Gordon and Kim Boedigheimer from Addison-Wesley for the production of the book.

# Modeling and Analysis with the AADL: The Basics

In this chapter, we illustrate the development of basic AADL models and present general guidance on the use of some of the AADL's core capabilities. With this, we hope to provide a basic understanding of architectural modeling and analysis and start you on your way in applying the AADL to more complex software-dependent systems.

While reading the first part of this chapter, you may want to use an AADL development tool to create the specifications and conduct the analyses described. OSATE supports all of the modeling and analyses discussed in this chapter.

# 3.1 Developing a Simple Model

In this section, we present a step-by-step development and analysis of an AADL model. Specifically, we model a control system that provides a single dimension of speed control and demonstrate some of the analyses that can be conducted on this architectural model. The speed control functionality is part of a powerboat autopilot (PBA) system that is detailed in Appendix A. While specialized to a powerboat, this model exemplifies the use of the AADL for similar control applications such as aeronautical, automotive, or land vehicle speed control systems.

The approach we use is introductory, demonstrating the use of some of the core elements and capabilities of the AADL. We do not include many of the broader engineering capabilities of the language. For example, we do not address packages, prototypes, or component extensions in developing this simple model. These are discussed later in this chapter. Instead, we proceed through the generation of a basic declarative model and its instance and show a scheduling analysis of the system instance. During your reading of this section, you may want to reference Part II for details on specific AADL elements or analyses used in the example.

Initially we create a high-level system representation using AADL system, process, and device components. Building on this initial representation, we detail the runtime composition of all of the elements; allocate software to hardware resources; and assign values to properties of elements to a level that is required for analysis and for the creation of an instance of the system. In these steps, we assume that requirements are sufficiently detailed to provide a sound basis for the architectural design decisions and trade-offs illustrated in the example. In addition, while we reference specific architectural development and design approaches that put the various steps into a broader context, we do not advocate one approach over another.

#### 3.1.1 Defining Components for a Model

A first step is to define the components that comprise the system and place their specification in packages. The process of defining and capturing components is similar to identifying objects in an object-oriented methodology. It is important to realize that components may include abstract encapsulations of functionality as well as representations of tangible things in the system and its environment. The definition of components is generally an iterative and incremental process, in that the first set of components may not represent a complete set and some components may need to be modified, decomposed, or merged with others.

First, we review the description of the speed controller for the PBA and define a simplified speed control model. In this model, we include a pilot interface unit for input of relevant PBA information, a speed sensor that sends speed data to the PBA, the PBA controller, and a throttle actuator that responds to PBA commands.

For each of the components identified, we develop type definitions, specifically defining the component's name, runtime category, and interfaces. Since we are initially developing a high-level (conceptual) model, we limit the component categories to system, process, and device.

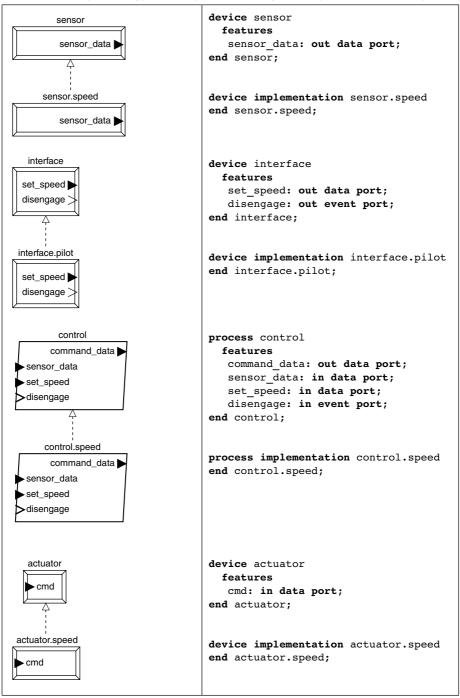

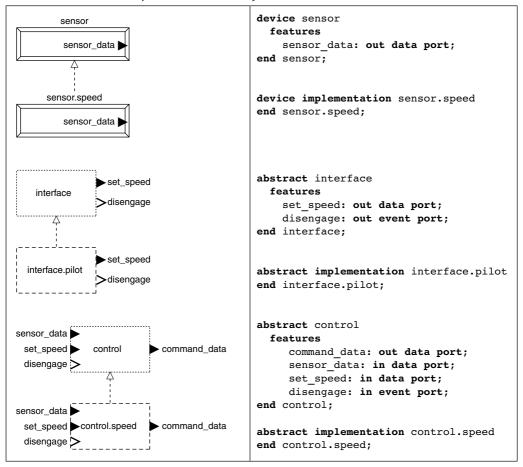

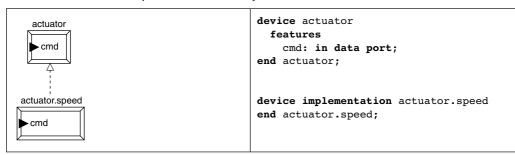

The initial set of components is shown in Table 3-1, where both the AADL text and corresponding graphical representations are included. For this example, the textual specifications of all of the components required for the model are contained in a single package and no references to classifiers outside the package are required. Thus, a package name is not needed when referencing classifiers. For the graphical representations, the implementation relationship is shown explicitly. Note that the icon for an implementation has a bold border when compared to the border of its corresponding type icon.

The speed sensor, pilot interface, and throttle actuator are modeled as devices and the PBA control functions are represented as a process. We use the devices category for components that are interfaces to the external environment that we do not expect to decompose extensively (e.g., a device can only have a bus as a subcomponent).

Devices in AADL can represent abstractions of complex components that may contain an embedded processor and software. With a device component, you represent only those characteristics necessary for analysis and an unambiguous representation of a component. For example, in modeling a handheld GPS receiver, we may only be interested in the fact that position data is available at a communication port. The fact that the GPS receiver has an embedded processor, memory, touch screen user interface, and associated software is not required for analysis or modeling of the system. Alternatively, a device can represent relatively simple external components, such as a speed sensor, whose only output is a series of pulses whose frequency is proportional to the speed being sensed. If you require a complex interface to the external environment, you can use a system component. In this case, you can detail its composition and as needed include an uncomplicated device subcomponent to represent the interface to the environment.

The use of a process component for the control functions reflects the decision that the core control processing of the PBA is to be implemented in software. The software runtime components will be contained within an implementation of this process type. The implementation declarations in Table 3-1 do not include any details. As

**Table 3-1:** Component Type and Implementations for the Speed Control Example

the design progresses, we will add to these declarations (i.e., adding subcomponents and properties as appropriate).

The interfaces for the PBA components are port features declared within a component type and are reflected in each implementation of that type. For example, the type *sensor* outputs a value of the speed via a data port *sensor\_data*. The pilot interface type *interface* provides a value for the set speed via a data port *set\_speed* and generates a signal to disengage the speed control via an event port *disengage*.

Notice that we have used explicit as well as abbreviated naming for the ports and other elements of the model (e.g., *command\_data* and *cmd* for the command data at input and output ports). The specificity of names is up to you, provided they comply with AADL naming constraints for identifiers (e.g., the initial character cannot be a numeral). Note that naming is case insensitive and *Control* is the same name as *control*.

In the PBA example, we have chosen to assign specific runtime component categories to each of the components (e.g., the speed sensor is a device). However, in real-world development as a design matures, the definition of these components may change (e.g., a component that computes the PBA speed control laws may initially be represented as a system and later modified to a process or thread). Using the approach we outline here, these changes are done manually within the AADL model (i.e., changing a system declaration to a process category declaration). An alternative approach is to use the generic abstract component category (i.e., not defining a specific runtime essence). Then later in the development, converting this abstract category into a specific runtime category employing the AADL extends capability (e.g., converting an abstract component to a thread). We have chosen to use the former approach to simplify the presentation and focus on decisions and issues related to representations of the system as concrete runtime components. A discussion of the use of the abstract component category is provided in Section 3.5.

For each of the component types we define a single implementation. These declarations are partial, in that we omit substantial details needed for a complete specification of the architecture. For example, we do not define the type of data that is associated with the ports. We will address these omissions as required in later steps. However, we can conduct a number of analyses for our simple example without including many of these details.

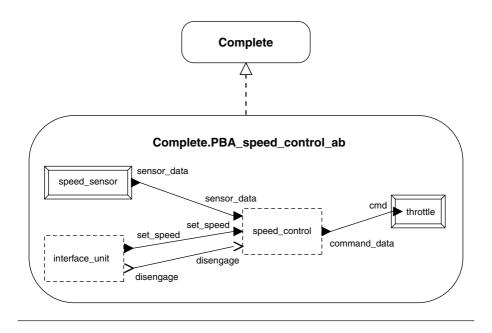

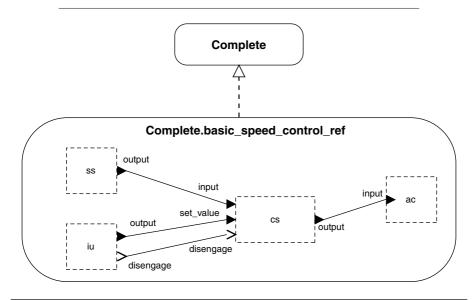

#### 3.1.2 Developing a Top-Level Model

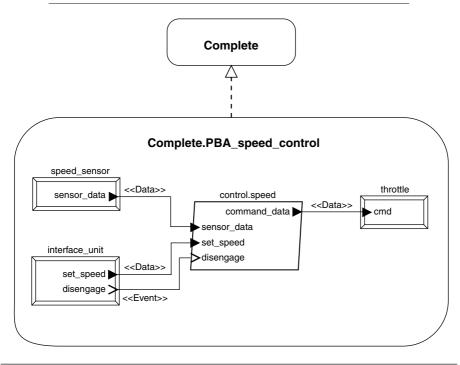

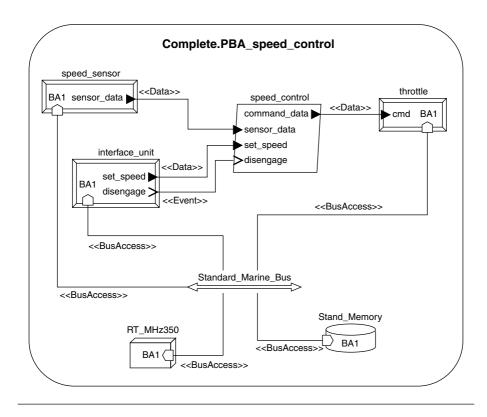

In the next step, we integrate the individual component implementations into a system by declaring subcomponents instances and their connections. We do this by defining an enclosing system type and implementation as shown in Listing 3-1, where we define a system type *Complete* and its implementation *Complete.PBA\_speed\_control*. There is nothing special about our choice of naming for this enclosing system. Another naming scheme, such as a type of *PBA* and an implementation of *PBA.speed*, would work as well.

Within the implementation, we declare four subcomponents. The three device subcomponents represent the speed sensor, throttle, and the pilot interface unit. The process subcomponent *speed\_control* represents the software that provides the speed control for the PBA. Notice that there are no external interfaces for the system type *Complete*. All of the interactions among the system's subcomponents are internal to the implementation *Complete.PBA\_speed\_control*, with the devices that comprise the system providing the interfaces to the external environment (e.g., sensors determining speed information from the vehicle).

Within the implementation, we define connections for each of the ports of the subcomponents. For example, connection *DC2* is the data connection between the *command\_data* port on the process *speed\_control* and the *cmd* data port on the device *throttle*. Each of the connections is labeled in the graphical representation shown in Listing 3-1 by the nature of the connection.<sup>1</sup> For example, connection *EC4* between the event port *disengage* on the *interface\_unit* device and the event port *disengage* on the *interface\_unit* device and the event port *disengage* on the speed\_control process is labeled as <*Event>>*. It is our choice to match most of the port names. It is not required that connected ports have the same name. However, they must have matching data classifiers if specified (they are omitted in this initial representation).

Listing 3-1: Subcomponents of the Complete PBA System

```

system Complete

end Complete;

system implementation Complete.PBA_speed_control

subcomponents

speed sensor: device sensor.speed;

```

<sup>1.</sup> The detailed graphical representation of the implementation *Complete.PBA\_speed\_ control* is taken from the OSATE environment.

```

throttle: device actuator.speed;

speed_control: process control.speed;

interface_unit: device interface.pilot;

connections

DC1: port speed_sensor.sensor_data ->

speed_control.sensor_data;

DC2: port speed_control.command_data -> throttle.cmd;

DC3: port interface_unit.set_speed ->

speed_control.set_speed;

EC4: port interface_unit.disengage ->

speed_control.disengage;

end Complete.PBA_speed_control;

```

Depending upon your development environment the graphical portrayals may differ from those shown in Listing 3-1. For example, within OSATE you cannot display the containment explicitly. Rather, the internal structure of an implementation is presented in a separate diagram that can be accessed hierarchically through the graphical icon representing the implementation *Complete.PBA\_speed\_control*.

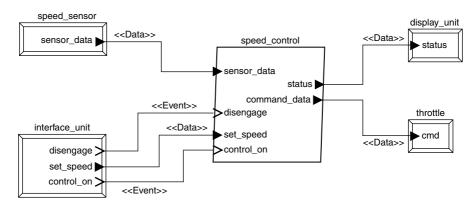

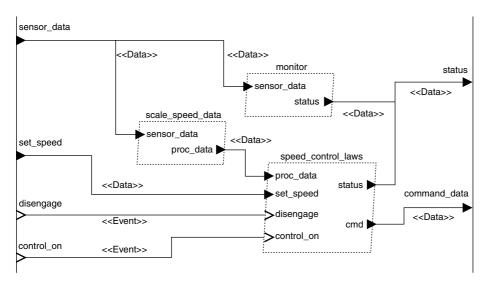

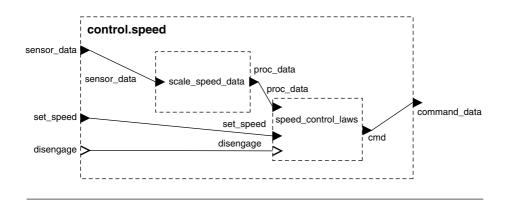

#### 3.1.3 Detailing the Control Software

At this point, we begin to detail the composition of the process *speed*\_ *control.* This involves decisions relating to partitioning the functionality and responsibilities required of the PBA system to provide speed control. Since we have treated the speed control as an autonomous capability, we have implicitly assumed that there are no interactions between the directional or other elements of the PBA and the speed control system. This may not be the case in advanced control systems. In addition, for the purposes of this example, we partition the functions of the speed control process into two subcomponents. The first is a thread that receives input from speed sensor; scales and filters that data; and delivers the processed data to the second thread. The second is a thread that executes the PBA speed control laws and outputs commands to the throttle actuator. Again, this simplification may not be adequate for a realistic speed control system (e.g., the control laws may involve extensive computations that for efficiency must be separated into multiple threads or may involve complex mode switches that are triggered by various speed or directional conditions)<sup>2</sup>.

Since the interfaces for the two threads are different, we define a type and implementation for each, as shown in Listing 3-2. We have used property associations to assign execution characteristics to the threads. Each is a periodic thread (assigned using the *Dispatch Protocol* property association) with a period of 50ms (assigned using the *Period* property association).

The assignment of periodic execution and the values for the period of the threads reflect design decisions. Generally, these are based upon the input of application domain and/or control engineers. The assignments we use here are not necessarily optimal but are chosen to provide specific values to enable analysis of system performance. They do not reflect the values for any specific control system.

Listing 3-2: PBA Control Threads Declarations

```

thread read_data

features

sensor_data: in data port;

proc_data: out data port;

```

<sup>2.</sup> In the next section we will demonstrate the addition of operational modes.

```

properties

Dispatch Protocol => Periodic;

Period => 50 ms;

end read data;

thread implementation read data.speed

end read data.speed;

thread control_laws

features

proc_data: in data port;

cmd: out data port;

disengage: in event port;

set_speed: in data port;

properties

Dispatch Protocol => Periodic;

Period => 50 ms;

end Control laws;

thread implementation control laws.speed

end control laws.speed;

```

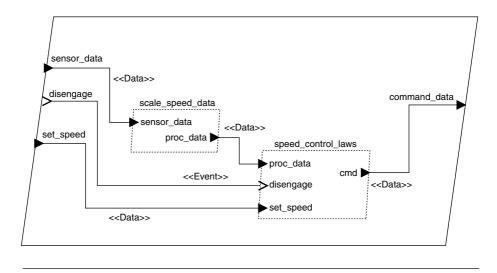

We detail the declaration of the process implementation *control.speed* that is presented in Table 3-1 to include the two thread subcomponents and their interactions (**connections**), as shown in Listing 3-3. There are five connections declared. Four of these connect ports on the boundary of the process with ports on the threads (i.e., *DC1*, *DC3*, *DC4*, and *EC1*). The fifth connects the out data port *proc\_data* on the thread *scale\_speed\_data* to the in data port *proc\_data* on the thread *speed\_control\_laws*.

**Listing 3-3:** The Process Implementation control.speed

```

process implementation control.speed

subcomponents

scale_speed_data: thread read_data.speed;

speed_control_laws: thread control_laws.speed;

connections

DC1: port sensor_data -> scale_speed_data.sensor_data;

DC2: port scale_speed_data.proc_data ->

speed_control_laws.proc_data;

DC3: port speed_control_laws.cmd -> command_data;

EC1: port disengage -> speed_control_laws.disengage;

DC4: port set_speed -> speed_control_laws.set_speed;

end control.speed;

```

continues

#### 3.1.4 Adding Hardware Components

At this point, we have defined the software components of the speed control system. We now define the execution hardware required to support the software. In modeling the hardware and binding the control software to that hardware, we can analyze the execution timing and scheduling aspects of the system.

In Listing 3-4, we define a processor, memory, and bus. The processor will execute the PBA control code (threads) and the memory will store the executable code (process) for the system. In addition, we have declared that the processor type *Real\_Time* and the memory type *RAM* require access to an instance of the bus implementation *Marine.Standard*. This bus will provide the physical pathway for the system. We will add properties to these declarations later in the modeling process.

Listing 3-4: Execution Platform Declarations

```

processor Real_Time

features

BA1: requires bus access Marine.Standard;

end Real_Time;

processor implementation Real_Time.one_GHz

end Real_Time.one_GHz;

memory RAM

features

BA1: requires bus access Marine.Standard;

end RAM;

```

```

memory implementation RAM.Standard

end RAM.Standard;

bus Marine

end Marine;

bus implementation Marine.Standard

end Marine.Standard;

```

#### 3.1.5 Declaring Physical Connections

To continue the integration of the system, we add instances of the required execution platform components into the system implementation *Complete.PBA\_speed\_control* by declaring subcomponents for the implementation. In addition, we declare that these components are attached to the bus. This is done by connecting the **requires** interfaces on the processor and memory components to the bus component.

Since the PBA control software executing on the processor must receive data from the sensors and pilot interface unit as well as send commands to the throttle actuator, we declare that these sensing and actuator devices are connected to the bus as well. To do this, we add **requires bus access** declarations in the type declarations for these three devices and connect them to the bus. The updated declarations for the three devices are shown in Listing 3-5 and the graphical representation of the system with the declaration of the physical (**bus access**) connections is shown in Listing 3-6.

**Listing 3-5:** Updated Device Declarations

```

device interface

features

set_speed: out data port;

disengage: out event port;

BA1: requires bus access Marine.Standard;

end interface;

device sensor

features

sensor_data: out data port;

BA1: requires bus access Marine.Standard;

end sensor;

```

continues

```

device actuator

features

cmd: in data port;

BA1: requires bus access Marine.Standard;

end actuator;

```

In Listing 3-6, we have defined a processor *RT\_1GHz*<sup>3</sup>, bus *Standard\_Marine\_Bus*, and memory *Stand\_Memory* as subcomponents. In addition, we have declared the connections for the bus *Standard\_Marine\_Bus* to the **requires bus access** features of each of the physical components (e.g., from *Standard\_Marine\_Bus* to *RT\_GHz.BA1* and to the **requires bus access** feature on the processor *RT\_1GHz.BA1*). The **requires access** features and the bus access connections are shown in the graphical representation in the lower portion of Listing 3-6.

**Listing 3-6:** Integrated Software and Hardware System

```

system implementation Complete.PBA speed control

subcomponents

speed sensor: device sensor.speed;

throttle: device actuator.speed;

speed_control: process control.speed;

interface unit: device interface.pilot;

RT 1GHz: processor Real Time.one GHz;

Standard Marine Bus: bus Marine.Standard;

Stand Memory: memory RAM.Standard;

connections

DC1: port speed_sensor.sensor_data ->

speed control.sensor data;

DC2: port speed control.command data -> throttle.cmd;

DC3: port interface_unit.set_speed ->

speed control.set speed;

EC4: port interface unit.disengage ->

speed control.disengage;

BAC1: bus access Standard Marine Bus <-> speed sensor.BA1;

BAC2: bus access Standard Marine Bus <-> RT 1GHz.BA1;

BAC3: bus access Standard Marine Bus <-> throttle.BA1;

BAC4: bus access Standard Marine Bus <-> interface unit.BA1;

BAC5: bus access Standard Marine Bus <-> Stand Memory.BA1;

end Complete.PBA speed control;

```

<sup>3.</sup> Since it is not the first character in the name, the numeric 1 can be used within the processor subcomponent name *RT\_1GHz*. However, an implementation name *Real\_Time.1\_GHz* is not legal, since the numeric is the first character in the implementation identifier.

#### 3.1.6 Binding Software to Hardware

In addition to specifying the physical connections, we bind software components to the appropriate physical hardware using contained property associations, as shown in Listing 3-7. These property associations are added to the system implementation declaration *Complete*. *PBA\_speed\_control*. The first two declarations allow the threads *speed\_control\_laws* and *scale\_speed\_data* to be bound to the processor *rt\_mhz500*. The reference part of the property association identifies the specific processor instance *rt\_mhz500* and the **applies to** identifies the specific thread in the hierarchy (e.g., *applies to speed\_control.scale\_speed\_data* identifies the thread *scale\_speed\_data* that is located in the process *speed\_control*. In this notation, a period separates the elements in the hierarchy.

We could have specified a specific binding using the *Actual\_ Processor\_Binding* property. However, the *Allowed\_Processor\_Binding* property permits scheduling tools to assign the threads to processors. For example, the resourced allocation and scheduling analysis plug-in that is available in the OSATE environment<sup>4</sup> binds threads to processors taking into consideration the threads' period, deadline, and execution time; processor(s) speed and scheduling policies; and the constraints imposed by the actual and allowed binding properties<sup>5</sup>. Specifically, if only allowed processor bindings are defined (i.e., the *Allowed\_Processor\_Binding* property), the plug-in schedules the thread onto processors and reports back the actual thread to processor bindings are defined (i.e., the *Allowed\_Processor\_Binding* property). If actual processor bindings are defined (i.e., the *Actual\_Processor\_Binding* property) the plug-in reports processor utilization based upon those bindings; allocates threads to processors; and runs a scheduling analysis to determine whether the bindings are acceptable.

Generally, a scheduling analysis or scheduling tool does scheduling analysis such that given a set of threads and their binding to processors (allowed or actual bindings), requisite attributes of the threads and processors (e.g., period, worst case execution time, processor cycle time, etc.), and defined scheduling policy, it determines if the set of threads meets the system's timing requirements. Typical scheduling policies include round-robin (RR), shortest job first (SJF), earliest deadline first (EDF), and rate monotonic (RM). The specific information required by and output from scheduling analysis tools vary.

The OSATE resource allocation and scheduling analysis plug-in makes binding decisions and in that process runs a scheduling analysis determining whether the binding is acceptable. This can be based on earliest deadline first (EDF) and rate monotonic scheduling (RMS) for periodic threads. In addition, it can conduct a rate monotonic analysis for periodic threads. This is useful for control system applications where all tasks are periodic, such as the PBA speed control example. In cases where threads are already bound to processors (i.e., using the *Actual\_Processor\_Binding* property), the plug-in determines schedulability for that specific deployment configuration.

If priority is assigned by hand and rate monotonic scheduling is used, another OSATE plug-in (priority inversion checker) enables the determination of whether the system has potential priority inversion. More sophisticated schedulability analysis tools are available for analyzing AADL models. A listing of these is available at https://wiki.sei. cmu.edu/aadl.

<sup>4.</sup> The resource allocation and scheduling analysis OSATE plug-in combines a binpacking algorithm with scheduling algorithms. The OSATE tool is available for download from www.aadl.info.

<sup>5.</sup> Some scheduling policies may require additional properties, such as explicit priority assignment. The scheduling tool in OSATE assumes all periodic tasks without shared logical resources; other scheduling tools, such as Cheddar, accommodate the full set of tasks in AADL including tasks with shared data components.

The third entry in Listing 3-7, binds the code and data within the process *speed\_control* to the memory component *Standard\_Memory*. We chose to use the actual rather than the allowed memory binding property, since there is only one memory component in the system and, while an additional processor might be added, we do not anticipate additional memory components to be added.

Listing 3-7: Binding Property Associations

```

properties

Allowed_Processor_Binding => (reference(RT_1GHz))

applies to speed_control.speed_control_laws;

Allowed_Processor_Binding => (reference(RT_1GHz))

applies to speed_control.scale_speed_data;

Actual_Memory_Binding => (reference(Stand_Memory))

applies to speed_control;

```

#### 3.1.7 Conducting Scheduling Analyses

Having defined the threads and established their allowed bindings to processors, we can begin to assess processor loading and analyze the schedulability of the system.

Before we proceed with a scheduling analysis, we define the requisite execution characteristics for the threads as they relate to the capabilities of the processors to which they may be bound. We specify this information through properties of the threads and processors. In this case, there is only one processor with an execution speed of 1GHz, as shown in Listing 3-8. Both threads are declared as *Periodic* with a period of 50ms. The default value in the AADL standard for the *Deadline* is the value of the *Period*. This value can be overridden by assigning a value to the *Deadline* using a property association. The execution time of the *read\_data* thread ranges from 1 millisecond (ms) to 2 milliseconds (ms), whereas the *control\_laws* thread's execution time ranges from 3ms to 5ms (as assigned using the *Compute\_Execution\_Time* property associations). These execution times are relative to the processor *Real\_Time. one\_GHz* declared in the model<sup>6</sup>.

<sup>6.</sup> If an AADL model has a single type of processor (i.e., only one processor speed) then the execution time is with respect to that processor. If there are multiple processors with different speeds, you can specify an execution time for each processor type (using in binding) or specify an execution time with respect to one of the other processors (the reference processor) using a scaling factor that is associated with each processor type. There is a *Reference\_Processor* property and a *Scaling\_Factor* property for this purpose.

Execution time estimates for the threads can be based upon timing measurements from prototype code or historical data for similar systems (e.g., systems with the same or comparable processors). By conducting the analysis early in the development process, you can get quantitative predictions of a system's performance. This information can be updated and re-evaluated as the design progresses. These early and continuing predictions can help to avoid last minute problems during code implementation and system integration (e.g., during testing when deadlines are not met because the processor loading exceeds the capability of the processor).

**Listing 3-8:** Updated Declarations for Analysis

```

thread read data

features

sensor_data: in data port;

proc data: out data port;

properties

Dispatch Protocol => Periodic;

Compute Execution Time => 1 ms .. 2 ms;

Period => 50 ms;

end read data;

thread control laws

features

proc data: in data port;

cmd: out data port;

disengage: in event port;

set speed: in data port;

properties

Dispatch Protocol => Periodic;

Compute Execution Time => 3 ms .. 5 ms;

Period => 50 ms;

end Control laws;

```

At this point, we have defined a declarative model for a simple speed control system including all of the components, properties, and bindings to describing a deployment configuration. From the top-level system implementation of this declarative model you create a system instance model and analyze it with the OSATE scheduler and scheduling analysis plug-in.

In Figure 3-1, we show the results of that analysis. It shows that the two threads in the system only use 14% of the processor capabilities. The worst case execution time for the two threads is 7ms, which is 14% of their 50 millisecond period.

| In system operation mode No Modes, all threads successfully bound to processors.      Processor Capacities Thread Bindings Message Bindings Network Capacities AADL Property Bin |     |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Processor Capacities Thread Bindings Message Bindings Network Capacities AADL Property Bin                                                                                       |     |

|                                                                                                                                                                                  | dir |

| Processor % Load % Available/Overload                                                                                                                                            |     |

Figure 3-1: Processor Capacities of the Speed Control System Instance

| Thread Binding Result                          | S                |                               | -                     | -                   |

|------------------------------------------------|------------------|-------------------------------|-----------------------|---------------------|

| In system operat                               | tion mode No Moo | des, all threads succe        | ssfully bound to proc | essors.             |

|                                                |                  |                               |                       |                     |

| Processor Capacities                           | Thread Bindings  | Message Bindings              | Network Capacities    | AADL Property Bindi |

| Processor Capacities                           | Thread Bindings  | Message Bindings<br>Processor | Network Capacities    | AADL Property Bindi |

| Processor Capacities<br>ance.speed_control.sca |                  | Processor                     | a)                    | AADL Property Bindi |

Figure 3-2: Bindings from the OSATE Scheduler and Scheduling Analysis Plug-in

Notice the information provided by the plug-in, including the actual binding for the threads determined by the plug-in (as shown in the cropped output of Figure 3-2).

#### 3.1.8 Summary

At this point, we have developed a basic architectural model of the PBA speed control system. In so doing, we have demonstrated some of the core capabilities of the AADL. For this relatively simple model, we analyzed the execution environment and made predictions of schedulability of the system. In subsequent sections, we describe additional capabilities of the AADL and discuss alternative modeling approaches that can be applied in this simple example.

# 3.2 Representing Code Artifacts

Within a comprehensive AADL architectural specification, source code files and related information needed for specifying and developing the

software within a system are documented using standard properties. These properties capture information for documenting architectural views such as code views [Hofmeister 00] and implementation views of allocation view types [Clements 10].

In this section, we document information relating to the PBA application software contained within the process control.speed. This excludes software that may be resident in the sensors, actuators, and interface devices as well as the operating system within the processor. First, we assume the application software has been written in a programming language, such as C or Java or in a modeling language, such as Simulink. We also assume that the software has been organized using the capabilities of the source language (e.g., by organizing Java classes and methods into packages with public and private elements). In this case, we can focus on specifying a mapping of the source files into the processes and threads of the application runtime architecture. Section 3.2.1 illustrates this mapping, which can be used to generate build scripts from the AADL model. Section 3.2.2 discusses how you can map identifier names used in AADL to identifier names that are acceptable in the source language. For larger systems, we may want to reflect not only the application runtime architecture in AADL, but also the modular source code structure. Section 3.2.3 illustrates how we utilize AADL packages for that purpose.

#### 3.2.1 Documenting Source Code and Binary Files

A modified excerpt of the PBA specification is shown in Listing 3-9. This includes a properties section within the implementation *control. speed*, where the property association for the property *Source\_Language* declares that the source code language for the implementation is C. This property is of type *Supported\_Source\_Languages*, which is defined in the property set *AADL\_Project* and has the enumeration values (Ada95, C, Simulink\_6\_5 are some examples). Property types and constants in the *AADL\_Project* property set can be tailored for specific projects. For example, languages such as Java can be added to the *Supported\_Source\_Languages* property type.

Using a property association for the newly defined property *Source\_Language*, the C language is declared as the programming language for all of the source code involved in the process *control.speed*. Two contained property associations for the property *Source\_Text* identify the source and object code files for the threads *speed\_control\_laws* and *scale\_speed\_data*. Two other contained property associations for the property

*Source\_Code\_Size* define the size of the compiled, linked, bound, and loaded code used in the final system.

In Listing 3-9, the data type *sampled\_speed\_data* is declared with a property association for the property *Source\_Data\_Size*. This property specifies the maximum size required for an instance of the data type. This data type is the classifier for the ports associated with the data that originates at the speed sensor.

Listing 3-9: PBA Specification with Code Properties

```

process implementation control.speed

subcomponents

scale speed data: thread read data.speed;

speed control laws: thread control laws.speed;

connections

DC1: port sensor data -> scale speed data.sensor data;

DC2: port scale speed data.proc data ->

speed_control_laws.proc_data;

DC3: port speed control laws.cmd -> command data;

EC1: port disengage -> speed control laws.disengage;

DC4: port set speed -> speed control laws.set speed;

properties

Source_Language => (C);

Source Text => ("ControlLaws.cc", "ControlLaws.obj")

applies to speed control laws;

Source Text => ("ScaleData.cc", "ScaleData.obj")

applies to scale_speed_data;

Source Code Size => 4 KByte applies to scale speed data;

Source Code Size => 10 KByte applies to speed control laws;

end control.speed;

```

## 3.2.2 Documenting Variable Names

A data port maps to a single variable in the application code. For example, the variable name for a data port can be specified using the *Source\_Name* property. This is shown in Listing 3-10, for the in data port *set\_speed* whose data classifier is the data type *set\_speed\_value*. The variable name for this port in the source code is *SetValue*.

We can use this mechanism to map data type and other component identifiers in an AADL model into the corresponding name in the source code. This is useful if the syntax of the source language allows characters in identifiers that are not allowed in AADL. We may also use this if we want to introduce more meaningful names in the AADL model for cryptic source code names.

Listing 3-10: Example of Documenting Variable Names

```

thread control_laws

features

proc_data: in data port;

cmd: out data port;

disengage: in event port;

set_speed: in data port set_speed_value

{Source_Name => "SetValue";};

properties

Dispatch_Protocol => Periodic;

Period => 50 ms;

end control_laws;

data set_speed_value

end set_speed_value;

```

#### 3.2.3 Modeling the Source Code Structure